3 Синтезируемое подмножество языка VHDL

После того как проектировщик убедился в корректности VHDL-модели цифровой системы, возникает проблема программной либо схемной реализации данной модели. Схемные реализации, как правило, являются более быстродействующими, поэтому важной задачей является задача синтеза схемы, функции которой реализуют поведение VHDL-модели. На практике, однако, переход к соответствующей логической схеме осуществляется не для всего языка VHDL, а только для некоторого подмножества этого языка, называемого синтезируемым подмножеством. Для VHDL-модели цифровой системы, описанной на синтезируемом подмножестве языка VHDL, можно получить схему. Обычно это интегральная схема типа ПЛИС либо схема, программируемая пользователем, вентильной матрицы. Общий метод получения такой схемы является компилятивным. Операторы языка VHDL заменяются компилятами. Компилят - это подсхема, реализующая вполне определенный оператор (конструкцию) языка, например, оператор сложения. При синтезе схемы типы данных bit отражаются при синтезе в проводники (полюса) схем, типы данных bit_vector - в шины (жгуты проводников). Перечислимые типы данных при синтезе кодируются булевыми векторами. Кодирование обычно ведется с использованием минимального числа кодирующих переменных. Например, для перечислимого типа

typemy_state is(RESET, IDLE, RW_CYCLE, INT_CYCLE);

может быть проведено кодирование

RESET = "00",

IDLE = "01",

RW_CYCLE = "10",

INT_CYCLE = "11".

Очевидно, в кодах 00, 01, 10, 11 используются только две кодирующие булевы переменные.

Компилятивный подход - не единственный для реализации алгоритмических описаний. Например, в работах ИТК НАН РБ предлагается способ схемной реализации параллельных процессов, описанных в терминах только двоичных переменных. Предложенный в ИТК НАН РБ язык описания параллельных процессов и способ схемной реализации базируются на мощном формализме сетей Петри.

Переменные языка VHDL, мгновенно передающие свои значения, исчезают при схемной реализации. В приведенном ниже примере проследите за переменной W в VHDL-коде и в соответствующей схеме (рис. 3.1).

Пример схемной "реализации" переменных языка VHDL.

Library IEEE;

use IEEE.std_logic_1164.all;

entity xor_var is

port (A,B,C : in std_logic;

X,Y : out std_logic);

end xor_var;

architecture example of xor_var is

begin

P : process (A,B,C)

variable W: std_logic;

begin

W := A; X <= C xor W;

W := B; Y <= C xor W;

end process;

end example;

|

|

Рис. 3.1 Исчезновение переменных при схемной реализации

Для логических операторов and, or, nand, nor, xor, xnor, not, над типами bit, boolean, arrays, bit_vector, компиляция в схему осуществляется прямым преобразованием логических выражений в соответствующие логические вентили (элементы).

Пример схемной реализации логических выражений.

entity logical_ops_l is

port (a, b, c, d: in bit; m: out bit);

end logical_ops_l;

architecture example of logical_ops_l is

signal e: bit;

begin

m <= (a and b) or e; — оператор назначения сигнала

e <= с xor d;

end example;

Схема, реализующая поведение объекта logical_ops_l, приведена на рис.3.2.

|

|

Рис. 3.2. Схемная реализация логического выражения для типа BIT

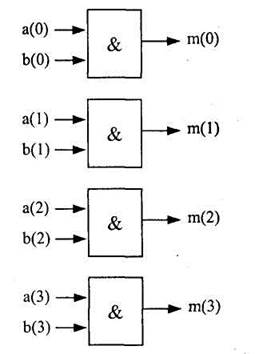

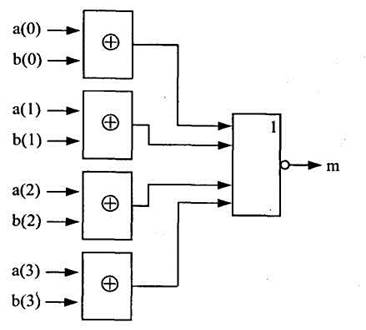

Пример схемной реализации логических выражений типа bit vector.

entity logical_ops_2 is

port (a, b: in bit_vector (0 to 3); m: out bit_vector

(0 to 3));

end logical_ops_2;

architecture example of logical_ops_2 is

begin

m <= a and b;

end example;

Соответствующая схема приведена на рис.3.3.

Рис. 3.3. Схемная реализация логического выражения для типа bit_vector

Схемная реализация операторов отношения

Операторами

отношения являются следующие операторы:

= (равно); /= (неравно); >

(больше); < (меньше); >= (больше или равно); <= (меньше или равно).

Операторы = , /= определяются в языке VHDL для всех типов. Операторы (>=, <=, >, < ) определяются для числовых типов, перечислимых типов и некоторых массивов. Результирующий тип всех операторов boolean. Следующие два примера показывают схемную реализацию для операторов a=b, a>=b.

entity relational_ops_l is

port (a, b: in bit_vector (0 to 3); m: out boolean);

end relational_ops_l;

architecture example of relational_ops_l is

begin

m <= a = b;

end example;

Схема, реализующая оператор равенства для типа bit_vector, приведена на рис.3.4.

Рис.3.4. Схемная реализация оператора a=b для типа bit_vector (0 to 3)

entity relational_ops_2 is

port (a, b: in integer range 0 to 3; m: out boolean);

end relational_ops_2;

architecture example of relational_ops_2 is

begin

m <= a >= b;

end example;

Схема, реализующая оператор >= для типа integer, показана на рис. 3.5.

Схемная реализация арифметических операторов

Арифметические операторы

+ (сложение);

- (вычитание);

* (умножение);

/ (деление);

mod(модуль);

rem(остаток);

abs(абсолютное значение);

** (возведение в степень)

определяются для числовых типов.

Операторы ( +, - ) являются достаточно "дорогостоящими" (дающими сложные схемы). Операторы (*, / , mod, rem) являются очень дорогостоящими. Обычно при синтезе делается специальная оптимизация, если справа от оператора находится константа или число, не большее 2. Реализация оператора (abs) не является сложной. Оператор (**) поддерживается только для констант.

|

|

Рис. 3.5. Схемная реализация оператора отношения а>=b для целых чисел a =(a3,a2,al,aO), b =(b3,b2,bl,b0)

Схемная реализация операторов управления

Схемным "аналогом" оператора if является, по существу, мультиплексор с одним управляющим входом, где b, с выступают в качестве настроечных входов, вход а - в качестве управляющего. Функционирование мультиплексора описывается следующей формулой:

m = а & с Va& b.

entitycontrolif is

port (a, b, c: boolean; m: out boolean);

end control_if;

architecture example of control_if is

begin

process (a, b, c)

variable n: boolean;

begin

if a then n := b;

else n := c;

end if;

m <= n;

endprocess;

endexample;

Можно привести схему, реализующую оператор if: если а=1, то m=b, если а=0, то m=с.

Однако не всегда очевидна та логическая схема, которая соответствует оператору языка VHDL. В качестве примера укажем на тот факт, что в компиляторах, осуществляющих схемную реализацию VHDL-кода, оператор if, у которого после ключевого слова else не производится никаких действий, интерпретируется как D-триггер (задержка). Поэтому получение нужных логических схем по VHDL-кодам с помощью САПР требует тщательного изучения библиотеки компилятов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.