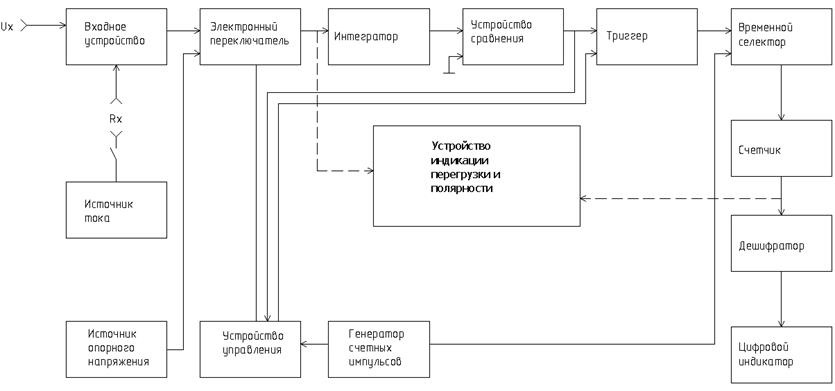

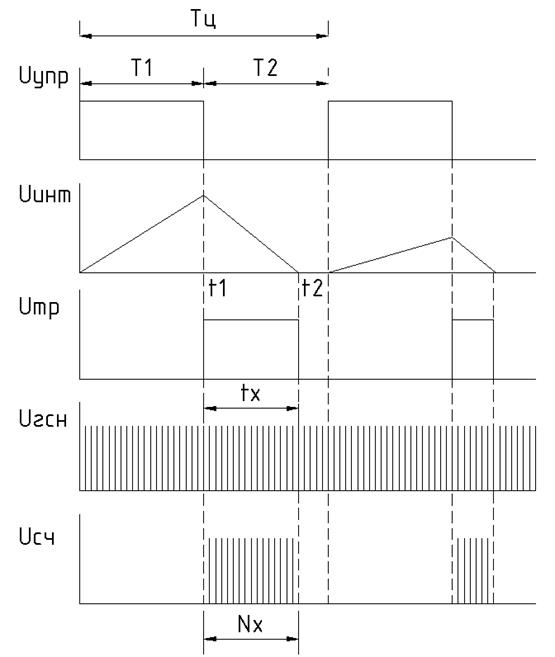

Длительность первого такта интегрирования равна длительности T1 управляющего импульса. В момент окончания импульса t1 триггер переключается из состояния ”0” в состояние ”1” и электронный переключатель отключает со входа интегратора источник измеряемого напряжения и соединяет вход интегратора с источником опорного напряжения Uоп, полярность которого противоположна полярности измеряемого напряжения. Начинается второй такт интегрирования, в течение которого напряжение на выходе интегратора линейно убывает. Скорость убывания этого напряжения пропорциональна значению опорного напряжения.

Момент t2, когда напряжение на выходе интегратора становится равным нулю, определяет окончание второго такта интегрирования. При этом срабатывает устройство сравнения, и триггер переводится из состояния ”1” в состояние ”0”.

С выхода триггера на один из выходов временного селектора поступает прямоугольный стробирующий импульс длительностью

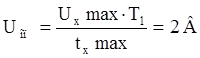

![]() (1)

(1)

(см. рис.2), который заполняется счетными импульсами, подсчитываемыми счетчиком. Их число пропорционально измеряемому значению напряжения. Цикл измерения закончен.

Начало следующего цикла задается фронтом очередного управляющего импульса T1, посылаемого управляющим устройством.

Рис.1. Структурная схема вольтомметра с двойным интегрированием

Рис.2. График, поясняющий принцип работы вольтомметра с двойным интегрированием

При работе цифровых вольтметров наиболее интенсивно проявляется сетевая помеха (fпом = 50 Гц). В вольтметре с двойным интегрированием высокий процент подавления сетевой помехи достигается рациональным выбором интервала интегрирования Т1, кратным периоду сетевой помехи [1 ]. Так как период измерения по условию равен 0,15с., то выберем период Т1 равным пяти периодам сетевой помехи:

![]()

Следовательно

![]() .

.

Примем максимальную длину стробирующего импульса равной Т2, т.е.

![]() .

.

Исходя из формулы, приведенной в литературе [1 ],

![]() (2)

(2)

можно найти значение опорного

напряжения при ![]() . и

. и ![]() :

:

Таким образом при напряжении на входе 1 В второй этап интегрирования будет длиться 0,05с. Этот промежуток времени необходимо заполнить счетными импульсами. Зададимся частотой счетных импульсов равной 20 кГц, т.е. период счетного импульса равен 0,00005с. Следовательно, на 1 Вольт будет потрачено 0,05/0,00005 = 1000 импульсов, 1 импульс соответствует напряжению 0,001 Вольт.

При использовании в устройстве индикации трех разрядов мы получим пределы измерения от 1 милливольта до 999 милливольт с точностью плюс-минус 1 милливольт, что составляет плюс-минус 0,1 процент. Итак, погрешность счета-индикации равна 0,1 процент.

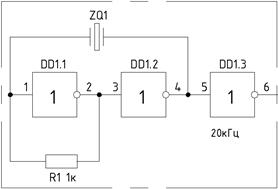

Генератор счетных импульсов (см. рис.3) состоит из логических элементов DD1.1 – DD1.3, для стабилизации частоты используется кварцевый резонатор ZQ1 на 20 кГц. В качестве логических элементов применены инверторы микросхемы К555ЛН1.

Элемент DD1.1 с помощью резистора ООС R1 равному 1 кОм выведен в линейный, усилительный режим, элемент DD1.3 применен как буферный, чтобы уменьшить влияние нагрузки на частоту генератора [2].

Рис.3. Схема принципиальная генератора счетных импульсов

Генератор управляющих импульсов состоит из (см. рис.4) делителя частоты на 4000, схемы формирования импульсов с частотой 0,6(6)Гц и скважностью 1.5, а также схемы управления электронным переключателем и счетчиком импульсов.

Делитель частоты на 4000 состоит из микросхемы DD2 – К555ИЕ5, и микросхем DD3-DD5 – К155ИЕ1. Микросхема К555ИЕ5 является четырехразрядным асинхронным счетчиком, для использования данной микросхемы в качестве делителя на 4, необходимо подавать входные импульсы на вход С0, а снимать выходную последовательность с выхода Q2, предварительно соединив выход Q0 с входом С1 микросхемы [2]. Деление частоты на 1000 осуществляется с помощью трех последовательно соединенных делителей на 10. Таким образом, на выходе делителя мы получаем частоту импульсов 5Гц со скважностью равной 2. Высокий уровень на выходе делителя представляет собой первый период интегрирования T1, низкий уровень, соответственно второй период интегрирования T2.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.