Делитель частоты, при подаче на его вход периодической импульсной последовательности, формирует на выходе такую же импульсную последовательность, но имеющую частоту повторений импульсов в заданное число раз меньше, чем по входной последовательности .

Построим ДЧ с коэффициентом деления равным 2. Для этого необходимо использовать один триггера и один триггер для запоминания выходного сигнала .

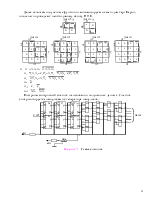

Составим таблицу состояний триггеров для данного делителя частоты :

Таблица 3 -- Таблица состояний делителя частоты

|

№ имп. |

Текущее состояние |

Последующее состояние |

Сигналы на информационных выходах |

|

Q |

Q |

D1 |

|

|

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

0 |

Отсюда получаем

![]()

Для подачи выходного сигнала мы используем триггер, на входы D которого необходимо всегда подавать единицу для того, чтобы он работал в качестве запоминающего устройства, выполняя функцию передачи выходного сигнала, а на вход С необходимо подавать сигнал который будет переключать этот триггер, снимаемый с триггера счётчика, равный коэффициенту счёта счётчика или коэффициенту деления делителя и передаваемый на вход С триггера.

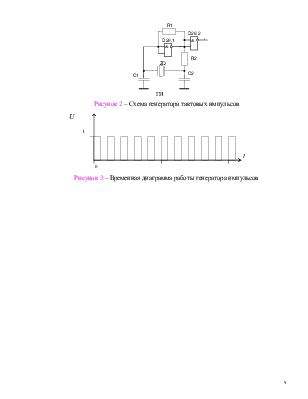

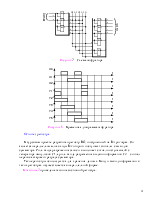

Схема делителя частоты с коэффициентом деления равным двум (кдел = 2 ) представлена на рисунке 5. а его временная диаграмма на рисунке 6.

Рисунок 5 - Схема делителя частоты

Рисунок 6 - Временная диаграмма делителя частоты

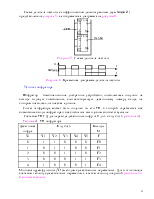

5 Синтез шифратора

Шифратор – комбинационное дискретное устройство, позволяющее получить на выходе кодовую комбинацию, соответствующую десятичному номеру входа, на котором появилась логическая единица.

Синтез шифратора может быть получен по его ТИ, в которой отражаются все возможные входы шифратора и все состояния выходов им соответствующие.

Составим ТИ СД для перевода десятичных цифр от 0 до 4 в код 2 из 5 (таблица 4).

Таблица 4 – ТИ шифратора

|

Десятичная цифра |

Код 2из5 |

Выходы М |

||||

|

Xi |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

F |

|

0 |

1 |

1 |

0 |

0 |

0 |

F0 |

|

1 |

0 |

1 |

1 |

0 |

0 |

F1 |

|

2 |

0 |

0 |

1 |

1 |

0 |

F2 |

|

3 |

0 |

0 |

0 |

1 |

1 |

F3 |

|

4 |

1 |

0 |

0 |

0 |

1 |

F4 |

Минимизируем функцию (Y1) методом существенных переменных. Для этого сначала составим таблицу существенных переменных, а затем таблицу покрытий (таблицы 5 и 6 соответственно).

Таблица 5 - Таблица существенных переменных для J2

|

Разрешенные наборы |

Запрещенные наборы |

Остатки |

|||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 6 – Таблица покрытий существенных переменных

|

Остатки |

Существенные переменные |

|

|

|

|

|

|

|

V |

V |

|

|

V |

|

В итоге получим:

![]()

Минимизируем остальные функции методом карт Карно.

![]()

![]()

![]()

![]()

Теперь можно на основании этих формул построить схему шифратора на рограмммируемой логической матрице. На основе таблицы истинности найдем функции алгебры логики выходов матриц.

Функции на выходе первой матрицы:

![]() ;

; ![]()

![]() ;

; ![]()

![]() ;

;

Функции на выходе второй матрицы:

![]() ;

; ![]()

![]() ;

; ![]()

![]() ;

;

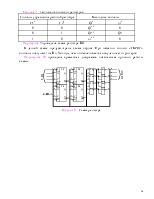

В результате получим схемку (рисунок 7).

Рисунок 7 – Схема шифратора

Рисунок 8 – Временная диаграмма шифратора

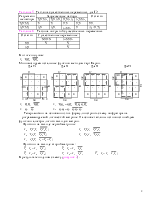

6 Синтез регистра

В курсовом проекте разработан регистр RG, построенный на D-триггерах. Он является параллельным, на входы D которого поступают сигналы с выходов сумматора. Роль входа разрешения записи выполняет сигнал поступающий с генератора импульсов С1, а роль входа разрешения выдачи информации С2 – сигнал переноса старшего разряда сумматора.

Такие регистры используются для хранения данных. Ввод и вывод информации в таких регистрах осуществляется в параллельной форме.

В таблице 7 приведена таблица состояний регистра.

Таблица 7 – таблица истинности регистров

|

Сигналы управления работой регистра |

Выходные сигналы |

||

|

С1n |

С2n |

Qin |

yin |

|

0 |

0 |

Qin-1 |

0 |

|

0 |

1 |

Qin-1 |

Qin |

|

1 |

0 |

xin-1 |

0 |

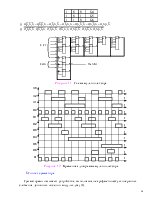

На рисунке 9 приведена схема регистра RG.

В данной схеме предусмотрена схема сброса. При нажатии кнопки «СБРОС» сигналы поступают на R и S входы, чем и обеспечивается обнуление его триггеров

На рисунке 10 приведена временная диаграмма, поясняющая принцип работы схемы.

Рисунок 9 - Схема регистра

Рисунок 10 - Временная диаграмма регистра

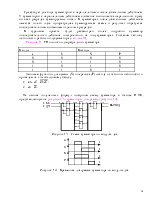

7 Синтез мультиплексора

Мультиплексор – комбинационное дискретное устройство, которое подключает к выходу тот из входов данных, номер которого задан на адресных входах при наличии сигнала синхронизации.

Построим асинхронный мультиплексор с семью входами данных, в качестве которых служат выходы со счетчика и один разряд регистра (вывод 64), и тремя адресными входами, т. е. выводы регистра 61, 62, 63. Для этого необходимо составить таблицу истинности (таблица 8), на основании которой запишем логическое

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.