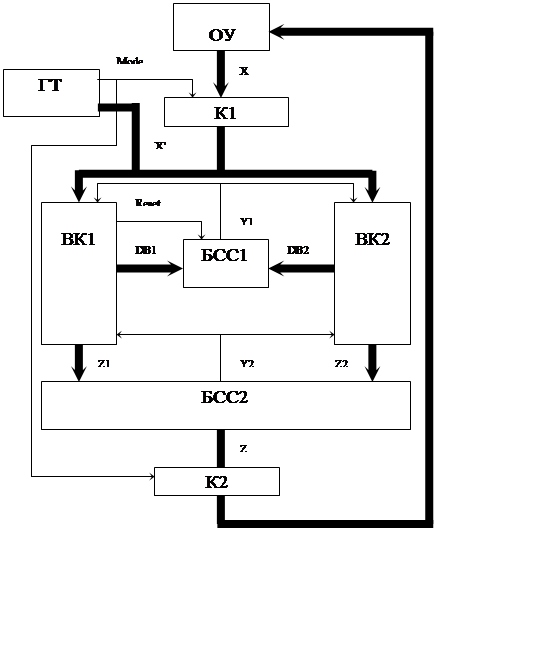

В тестовом режиме ГТ отключает вычислительные каналы от ОУ и имитирует ОУ, посылая сигналы X’ вместо X. Работа вычислительных каналов и безопасных схем сравнения при этом ничем не отличается от их работы в рабочем режиме.

|

Рисунок 1 - Структурная схема МПС

Микропроцессор КР580ВМ80 является однокристальным восьмиразрядным микропроцессором, выполненного по технологии n-МОП [4]. Для работы КР580ВМ80 необходимы три источника питания: -5 В, +5 В, +12В. Кристалл микропроцессора, содержащий около 5000 транзисторов, расположен в корпусе, имеющем 40 выводов [3]. КР580ВМ80 обладает однонаправленная шестнадцатиразрядная шина адреса и двунаправленная восьмиразрядная шина данных. Кроме этого имеется 12 сигнальных линий (шесть входных и шесть выходных).

Наличие шестнадцатиразрядной шины адреса позволяет адресовать 64 Кбайта памяти. Используя сигнальные линии INT и INTA в МПС можно применить контроллер прерываний, а благодаря наличию линий HOLD и HLDA можно организовать режим прямого доступа к памяти. Для работы с медленнодействующими модулями памяти используется сигнал XACK.

Для синхронизации работы процессора с памятью и другими внешними устройствами применяется генератор тактовых импульсов КР580ГФ24. Частота следования синхроимпульсов F1 и F2 в девять раз меньше частоты кварцевого резонатора. Для получения оптимальной для микропроцессора тактовой частоты 2 МГц используется кварцевый резонатор частотой 18 МГц. Сопротивление кварцевого резонатора носит индуктивный характер. Это приводит к нестабильной работе генератора. Для компенсации ёмкостной составляющей резонатора последовательно с ним включается конденсатор емкостью 20 пФ [1].

Для обеспечения достаточной нагрузочной способности шин микропроцессора необходимо применить шинные формирователи. В качестве таковых будем использовать регистры КР580ИР82.

Исходные данные для организации подсистемы ПЗУ и ОЗУ приведены в таблице 1.

Таблица 1

|

Тип памяти |

Емкость, Кбайт |

Организация БИС |

Входы выборки кристалла |

Использование READY |

Тип БИС |

|

ПЗУ |

2 |

1024*4 |

CS0, CS1 |

Нет |

КР556ЗЕ13 |

|

ОЗУ |

4 |

2К*8 |

CS0, CS1 |

Нет |

КР537РУ8 |

Исходя из таблицы 1 делаем вывод, емкость ПЗУ нужно наращивать по смешанному (вертикально-горизонтальному) типу, а ОЗУ – по горизонтальному. Нет необходимости использовать сигнал READY так как БИС обладают достаточным быстродействием.

Для организации выбора БИС в качестве дешифратора применим БИС ПЗУ К556РТ5, запрограммированной в соответствии с таблицей 2.

Таблица 2

|

Адресное пространство |

БИС |

Адрес ПЗУ |

Данные в ПЗУ |

|

0000 – 03FF |

ПЗУ1, ПЗУ2 (чтение) |

01 |

07F |

|

0400 – 07FF |

ПЗУ3, ПЗУ4 (чтение) |

05 |

0BF |

|

0800 – 0FFF |

ОЗУ1 (чтение) |

09, 0D |

0DF |

|

ОЗУ1 (запись) |

0A, 0E |

0D0 |

|

|

1000 – 17FF |

ОЗУ2 (чтение) |

11, 15 |

0EF |

|

ОЗУ2 (запись) |

12, 16 |

0E0 |

Для обращения к внутренним регистрам периферийных БИС будем использовать команды чтения/записи из/в память. Выбор соответствующих БИС (ППА, ПСА, ПИТ, ПКП, регистры для индикации - РИ и ввода кода уставки - РК) будем осуществлять при помощи дешифратора К155ИД3. Каждой БИС соответствует четыре байта в ОЗУ. Адреса ОЗУ для обращения к регистрам БИС приведены в таблице 3.

Таблица 3

|

Адресное пространство |

Периферийная БИС |

|

8000 – 8003 |

ПКП |

|

8004 – 8007 |

ППА |

|

8008 – 800B |

ПСА |

|

800C – 800F |

ПИТ |

|

8010 – 8013 |

РИ1 |

|

8014 – 8017 |

РИ2 |

|

8018 – 801B |

РИ3 |

|

801C – 801F |

РИ4 |

|

8020 – 8023 |

РК |

|

8024 - 8028 |

Выходной регистр |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.