В первой позиции окна «Type the name of the source file to create» указываем имя файла, в котором будет храниться создаваемая схема, в окне «Type the name of the Entity» указываем имя интерфейса схемы, а в окне «Type the name of the architecture body» - имя модуля её архитектуры, и нажимаем клавишу «Далее».

В окне «New Source File Wizard - Ports» указываем требуемое количество входных и выходных портов и присваиваем им идентификаторы. Добавление выполняется кнопкой New. Входные порты задаются указателем In, а выходные - Out, в левом окне вывода увидим формирование входных и выходных портов устройства. После описания портов нажать клавишу «Готово». На появившемся графическом поле мы увидим шаблон проекта с входными и выходными портами.

Для подготовки схемы необходимо выбрать пункт меню View – Symbols Toolbox. В появившемся в правой части экрана окне необходимо развернуть список типовых элементов Built-inSymbols (или специализированной библиотеки, например, Virtex), из которого на поле редактирования разместить необходимые элементы и соединить их в схему. Соединение элементов выполняется опцией, выбираемой из меню Diagram – Wire, или соответствующей кнопкой на передней панели пакета.

Далее файл необходимо скомпилировать, для чего необходимо указать правой клавишей Мышки на имя файла в «Design Browser» и из контекстного меню выбрать пункт Compile. При успешной компиляции возле имени файла в окне «Design Browser» появится галочка. Развернув иерархию файла можно увидеть имя файла с кодом VHDL, содержимое которого необходимо просмотреть (двойное нажатие левой клавиши мыши на имени файла) и сравнить с собственной программой.

2.4 Задание тестовых воздействий для моделирования

Для подготовки моделирования и задания тестовых воздействий в окне «Design Browser» раскрыть иерархию файлов, правой клавишей мыши указать на имя скомпилированного файла (с красной иконкой), с которым планируется работа, и из контекстного меню выбрать команду «Set as Top-Level». Далее необходимо задать тестовые воздействия, для чего выбрать пункт меню File-New-Waveform, а в появившемся на верхней панели меню Waveform выбрать AddSignalsи, указывая курсором Мышки на порты и именованные узлы, кнопкой Add выбрать все требуемые порты и узлы схемы, после чего закрыть окно AddSignalsкнопкойClose.

В появившемся окне WaveformEditor двойным нажатием левой клавишей в столбце Stimulator или нажатием правой клавишей мыши на строке в колонках Name или Value каждого входного! сигнала, выбрать опцию Stimulator.

В окне Stimulatorsуказать тип (опция Type) тестового сигнала и нажать клавишу Apply, т.е. «Применить». Для первоначального освоения рекомендуются типы Custom (предпочтительно) или Clock (несколько сложнее в освоении). Для Clockможно задавать начальное значение сигнала, начальное смещение, частоту или период и скважность.

Перед заданием входных воздействий надо проинициализировать моделирование проекта, иначе пакет не позволяет редактировать входные сигналы. Для инициализации необходимо вызвать последовательно пункты меню Simulation-InitializeSimulation, и затем сразу жеSimulation - EndSimulation.

После выполнения инициализации переходим в режим редактирования сигналов : Waveform – EditMode. В режиме редактирования следует курсором Мышки на поле диаграммы каждого входного сигнала отметить требуемые участки времени для входных портов и клавишами «1» или «0» установить требуемые логические значения.

2.5 Моделирование схемы

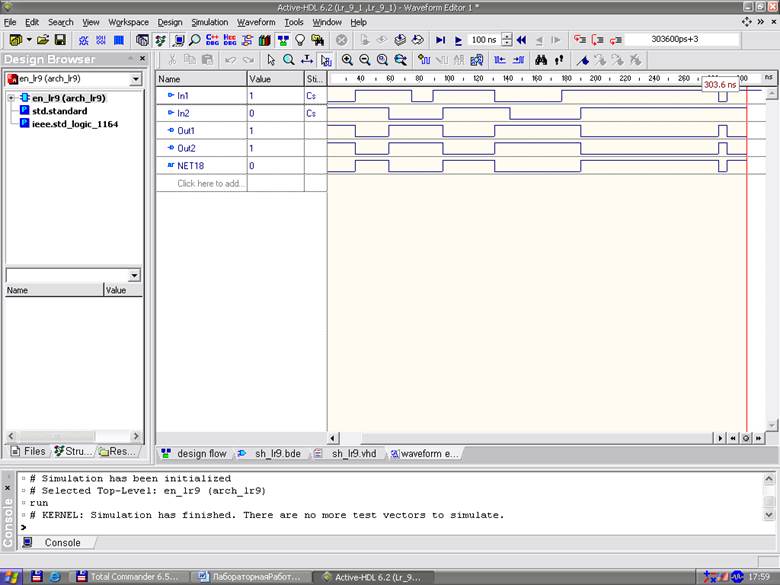

Процесс моделирования инициализируется пунктами меню Simulation-InitializeSimulation. Далее необходимо выполнить непосредственно моделирование командами Simulation- Run или Simulation- RunUntil(в этом случае можно явно указать время моделирования).

В результате пакет выполнит моделирование схемы:

После окончания процесса

моделирования необходимо выполнить операцию окончания моделирования: Simulation – EndSimulation.

После окончания процесса

моделирования необходимо выполнить операцию окончания моделирования: Simulation – EndSimulation.

2.6 Получение результатов моделирования в виде таблицы

Для просмотра результатов моделирования в форме таблицы выполнить следующие команды: File – New – List.

На появившемся поле вывода правой клавишей мыши вызвать контекстное меню, из которого выбрать пункт AddSignals и кнопкой Add добавить все интересующие сигналы в поле таблицы, указывая на них курсором Мышки. Далее запустить моделирование по аналогии с п.5, при этом, возможно, потребуется выполнить команды Simulation- RestartSimulation и затем Run. В таблице появится набор логических состояний схемы, зафиксированных при смене входных воздействий.

3 Подготовка отчёта по лабораторной работе

Отчёт должен содержать:

- исходное задание к лабораторной работе;

- текст программы;

- схемы, подготовленные в редакторе схем;

- VHDL-код, полученный при компиляции графической схемы;

- результаты моделирования в виде временной диаграммы и таблицы;

- развёрнутые выводы по работе.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.