Выполнил студент группы ЭМ-51 Ульянченко С.Н.

Лабораторная работа №5

Проектирование АЛУ

Цель работы: получить практические навыки в проектировании простейших арифметико-логических устройств, входящих в состав устройств , реализуемых на базе ПЛИС.

Индивидуальное задание:

|

Вариант |

Операция 1 |

Операция 2 |

Операция 3 |

|

8 |

+ |

not |

shr |

Текст на VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity ystroistvo is

Port ( Vhod_1 : in STD_LOGIC_VECTOR (7 downto 0);

Vhod_2 : in STD_LOGIC_VECTOR (7 downto 0);

Operac : in STD_LOGIC_VECTOR (1 downto 0);

CLK : in STD_LOGIC;

Z : out STD_LOGIC;

Vihod : out STD_LOGIC_VECTOR (7 downto 0);

CY : out STD_LOGIC;

OV : out STD_LOGIC;

P : out STD_LOGIC );

end ystroistvo;

architecture Behavioral of ystroistvo is

signal Z1: std_logic_vector (7 downto 0):= "00000000";

signal res: std_logic_vector (7 downto 0):= "00000000";

begin

proc1:process(CLK) is

variable number1:integer;

variable number2:integer;

variable b:integer;

variable p1:STD_LOGIC;

begin

if CLK='1' and CLK'event then

if Operac="01" then

number1 := conv_integer( unsigned( Vhod_1 ) );

number2 :=conv_integer( unsigned( Vhod_2 ) );

b := number1 + number2;

Z1 <= std_logic_vector( conv_unsigned ( b,8 ) );

Vihod <= std_logic_vector( conv_unsigned ( b,8 ) );

if Z1="00000000" then

Z <= '1';

else Z <= '0';

end if;

if ( 255-number1) < number2 then

CY <= '1';

else CY <= '0';

end if;

p1 :=(Z1(7) xor Z1(6) xor Z1(5) xor Z1(4) xor Z1(3) xor Z1(2) xor Z1(1) xor Z1(0));

if p1 ='0' then

p <= '1';

else p <= '0';

end if;

end if;

if Operac="10" then

Vihod <= not(Vhod_1);

Z1 <= not(Vhod_1);

if Z1="00000000" then

Z <= '1';

else Z <= '0';

end if;

p1 :=(Vhod_1(7) xor Vhod_1(6) xor Vhod_1(5) xor Vhod_1(4) xor Vhod_1(3) xor Vhod_1(2) xor Vhod_1(1) xor Vhod_1(0));

if p1 ='0' then

p <= '1';

else p <= '0';

end if;

end if;

if Operac="11" then

res(7) <= '0';

res(6) <= Vhod_1(7);

res(5) <= Vhod_1(6);

res(4) <= Vhod_1(5);

res(3) <= Vhod_1(4);

res(2) <= Vhod_1(3);

res(1) <= Vhod_1(2);

res(0) <= Vhod_1(1);

Vihod <= res;

p1 :=(res(7) xor res(6) xor res(5) xor res(4) xor res(3) xor res(2) xor res(1) xor res(0));

if p1 ='0' then

p <= '1';

else p <= '0';

end if;

if Vhod_1(7)='1' and Vhod_1(6)='1' and Vhod_1(5)='1' and Vhod_1(4)='1' and Vhod_1(3)='1' and Vhod_1(2)='1' and Vhod_1(1)='1' and Vhod_1(0)='1' then

CY <= '1';

else CY <= '0';

end if;

end if;

end if;

end process;

end Behavioral;

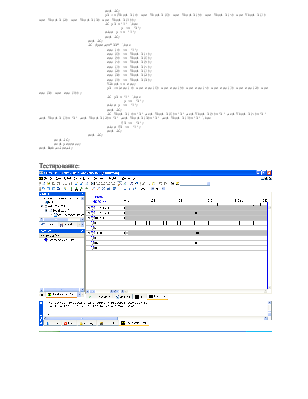

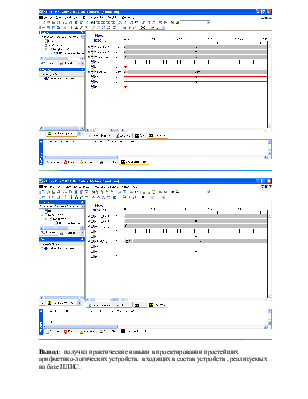

Тестирование:

Вывод: получил практические навыки в проектировании простейших арифметико-логических устройств, входящих в состав устройств , реализуемых на базе ПЛИС.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.