Основные элементы и конструкции языка VHDL

1 Модели описания цифровой системы

Цифровая система может быть описана на уровне поведения, т.е. функций, реализуемых системой, и на структурном уровне. Таким образом, основные модели описания – структурная и функциональная. Функциональную модель называют также поведенческой.

Структурное описание - это описание системы в виде совокупности компонент (подсхем, элементов) и связей между компонентами.

Функциональное (Поведенческое) описание - это описание системы при помощи некоторых процедур на уровне зависимостей выходов от входов. Иначе говоря, поведенческое описание задает алгоритм, реализуемый системой. Поведенческое (его иногда называют функциональным) удобно использовать, например, при описании таблиц истинности.

В литературе можно встретить классификацию функционального (поведенческого) описания на описание в виде потока данных (data flow) и процедурное описание.

Заметим, что помимо указанных моделей при спецификации цифровых систем допустим смешанный стиль, что весьма удобно при создании моделей и проектировании дискретных устройств.

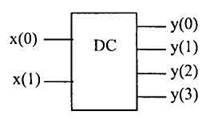

Рассмотрим различные модели описания одного и того же поведения на примере дешифратора DC, который имеет два входных полюса и четыре выходных (рис. 1.1).

Рис. 1.1. Дешифратор

Функции дешифратора имеют следующий вид:

y(0) = not(x(0)) and not(x(1))

y(1) = not(x(0)) and x(1)

y(2) = x(0) and not(x(1))

y(3) = x(0) and x(1)

На рис. 1.1 слева и справа указаны имена входных и выходных полюсов, употребляемых в VHDL описании.

Опишем интерфейс дешифратора:

entity Decoder is

port (X: in Bit_vector (0 to 1);

Y: out Bit_vector (0 to 3));

end Decoder;

Теперь покажем различные модели (стили) описания функционирования |дешифратора: строго структурное описание, описание в виде потомка данных, процедурное описание.

Структурное описание архитектурного тела в виде схемы в базисе инверторов (Inverter) и двухвходовых элементов И (AND_Gate) имеет вид:

architecture structure of Decoder is

signal S: Bit_vector (0 to 1);

component AND_Gate port (A, B: in Bit; D: out Bit);

end component;

component Inverter port (A: in Bit; B: out Bit);

end component;

begin

Inv1: Inverter port map (A=>x(0), B=>s(0));

Inv2: Inverter port map (A=>x(1), B=>s(1));

A1:AND_Gate port map (A=>s(0), B=>s(1), D=>y(0));

A2:AND_Gate port map (A=>s(0), B=>x(1), D=>y(1));

A3:AND_Gate port map (A=>x(0), B=>s(1), D=>y(2));

A4:AND_Gate port map (A=>x(0), B=>x(1), D=>y(3));

end structure;

В структурном описании схемы в базисе инверторов (Inverter) и двухвходовых элементов И (AND_Gate) в начале входные сигналы инвертируются, при этом они записываются в промежуточный вектор, т.е. вектор внутренних сигналов S. А затем выполняются операции И на двухвходовых элементах AND_Gate. Таким образом, очевидно, реализованы заданные функции дешифратора.

Описание поведения дешифратора в виде потока данных (data flow):

entity Decoder is

port (X: in Bit_vector (0 to 1);

Y: out Bit_vector (0 to 3));

end Decoder;

architecture Data_flow of Decoder is

begin

y(0) <= not x(0) and not x(1);

y(1) <= not x(0) and x(1);

y(2) <= x(0) and not x(1);

y(3) <= x(0) and x(1);

end Data_flow;

Процедурное описание дешифратора выглядит следующим образом:

entity Decoder is

port (X: in Bit_vector (0 to 1);

Y: out Bit_vector (0 to 3));

end Decoder;

architecture Procedural of Decoder is

signal s: bit_vector (0 to 3);

begin

process (x, s)

begin

case x is

when "00"=> s<= "1000";

when "01"=> s<= "0100";

when "10"=> s<= "0010";

when "11"=> s<= "0001";

end case;

end process;

y<=s;

end Procedural;

Процедурное описание, как нетрудно видеть, удобно использовать для программирования объектов, заданных таблицами истинности.

Смешанное описание, использующее элементы структурного описания и элементы описания "поток данных", приведено ниже.

architecture Mixed of Decoder is

component Inverter port (A: in Bit; B: out Bit);

end component;

signal S: bit_vector (0 to 1);

begin

Inv 1: Inverter port map (A=>x(0), B=>s(0));

Inv2: Inverter port map (A=>x(l), B=>s(l));

p: process (s, x)

begin

y(0)<=s(0) and s(l);

y(l)<=s(0) and x(l);

y(2)<=x(0) and s(l);

y(3)<=x(0) and x(l));

end process;

end Mixed;

В данном примере структурное описание и описание типа "поток данных" весьма схожи, так как происходит замена логических элементов (компонентов) логическими выражениями. Однако для сложных схем такая замена может быть совершенно не очевидной.

2 Структура описания архитектурного тела (Architecture) VHDL

Язык VHDL в силу того, что это в первую очередь язык описания аппаратуры чрезвычайно структурирован. Поэтому рекомендуется следовать предписаниям и рекомендациям стандарта языка при подготовке моделей и программ на VHDL.

Структура блока Architectureсогласно стандарта строится следующим:

Декларация компонент и внутренних сигналов

Параллельные операторы:

Конкретизация компонента

Назначение сигнала

Операторы параллельного вызова процедур, условного назначения сигналов, конкретизации компонента

Операторы Block, Assert, Select, Generic

Оператор генерации Generate

Оператор процесса Process, который включает:

Декларации переменных

Последовательные операторы

Назначение сигнала

Присваивание значения переменной

Вызов процедуры

Оператор ожидания Wait

Оператор If, Case, Loop, Next и т.д.

Так как VHDL – язык описания аппаратуры, то предполагается, что основные операции выполняются параллельно. Поэтому следует различать операторы и конструкции языка, которые выполняются параллельно и те, которые могут выполняться последовательно.

ВVHDL последовательные операторы подобны операторам языков высокого уровня. Из общей структуры описания архитектурного тела следует, что последовательные операторы (sequential statement) могут появляться только внутри операторов процесса, а также внутри тел подпрограмм (функций, процедур).

Перечислим последовательные операторы:

1) оператор присвоения значения переменной;

2) оператор назначения сигнала, т.е. присвоения значения сигналу;

3) оператор if (если);

4) оператор case (случай);

5) оператор loop (цикл);

6) оператор next (следующий);

7) оператор exit (выход);

8) оператор null (нуль, пустой);

9) оператор вызова процедуры;

10) оператор return (возврат);

11) оператор assert (сообщение);

12)оператор wait (ожидать)

Перечислим основные параллельные операторы:

1.Process(процесс);

2.Generate(генерации);

3. Параллельного сообщения;

4. Параллельного вызова процедуры;

5. Условного назначения сигнала;

6. Выборочного назначения сигнала Select;

7. Конкретизации (создания экземпляра) компонента;

8. Block.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.