Каждый запрос шлейфа может быть индивидуально замаскирован с помощью программно-доступного по записи триггера маски MSK.. Обычно этот триггер входит в состав CW устройства и доступен для обратного контроля через SW. Вектор прерывания устройства может быть как фиксированным, так и программно-управляемым. При использовании шлейфа совместно с ЦП на базе ВМ80 вектор имеет вид 11NNN111, соответствующий команде RSTN, N=0—7.

Основной недостаток шлейфовой структуры—трудность управления приоритетами. Устройства, стоящие в INTA-цепочке ближе к ЦП, обладают более высоким приоритетом, поэтому изменение приоритетов сводится к изменению последовательности опроса, для чего может потребоваться специальная логика арбитража. Последняя может выполняться как централизованными, так и децентрализованными средствами.

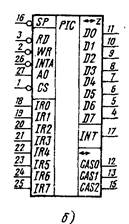

3.6. Программируемый контроллер прерываний ВН59

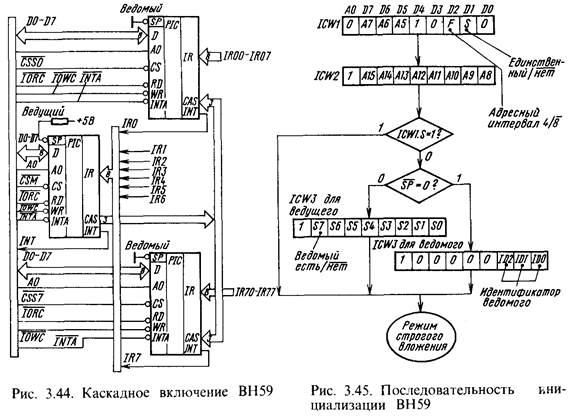

Система векторных прерываний ВМ80/ВМ85А может быть построена различными способами. Наиболее эффективно она реализуется с помощью специальной БИС типа КР580ВН59 (ВН59), называемой программируемым контроллером прерываний (ПКП). Микросхема выполняется по п-МОП-технологии и размещается в 28-выводном корпусе с вертикальным расположением выводов. Она совместима с ТТЛ-схемами. Для работы БИС требуется единственный источник питания +5 В.

На основе ПКП ВН59 формируется 8-уровневая приоритетная система векторных прерываний для МП типов ВМ80/ВМ85А. Несколько контроллеров ВН59 могут соединяться каскадно для расширения числа уровней прерывания до 64. Прибор обеспечивает работу в нескольких режимах, позволяя оптимизировать

|

|

логику работы системы прерываний согласно требованиям, предъявляемым к МС. Структурная схема и условное графическое обозначение ПКП приведены на рис. 3.41. •-' Рассмотрим работу ВН59 в автономном режиме (рис. 3.42). Один или несколько запросов на прерывания (переход из 0 в 1) подаются на входы 1RO—IR7 и запоминаются в регистре запросов IRR (Interrupt Request Register). Регистр обслуживания ISR (In Service Register) содержит все запросы, которые в данное время находятся в стадии обработки. Регистр маски IMR (Interrupt Mask Register) используется для маскирования отдельных уровней. Запрет некоторого уровня соответствует единице в соответствующем разряде IMR.

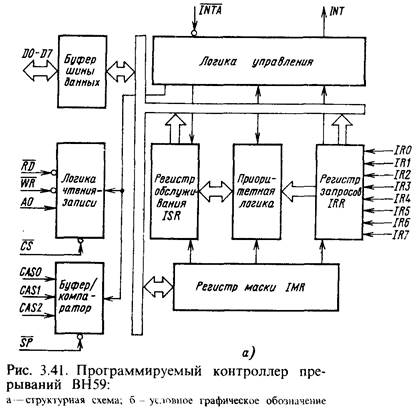

Приоритетная логика выбирает разрешенный запрос на прерывание с наивысшим приоритетом из числа поступивших и сравнивает его с текущим приоритетом запросов, находящихся на обслуживании. При превышении последнего ПКП генерирует сигнал INT (рис. 3.43). Микропроцессор подтверждает прием запроса INT генерацией строба 1NTA, под воздействием которого запрос с высшим приоритетом из IRR фиксируется в соответствующем разряде ISR. Принятый к обслуживанию IRR-бит сбрасывается и прием нового запроса разрешается. Одновременно с этим ПКП генерирует код команды CALL (OCDH), который принимается МП. В ответ ВМ80/ВМ85А инициирует еще два следующих друг за другом INTA-цикла. Во время этих циклов ПКП передает в МП полный адрес программы обслуживания прерывания, принятого к обработке: сначала младший, а затем старший байт адреса. Установленный в ISR бит остается в состоянии 1 до окончания процедуры обслуживания. В конце процедуры в ПКП

должна быть передана специальная команда окончания прерывания EOI, которая сбрасывает соответствующий ISR-бит.

До тех пор, пока некоторый ISR-бит установлен, все запросы с равным или меньшим приоритетом игнорируются. В то же время запросы с более высоким приоритетом приводят к генерации сигнала INT, инициируя вложенные прерывания МП.

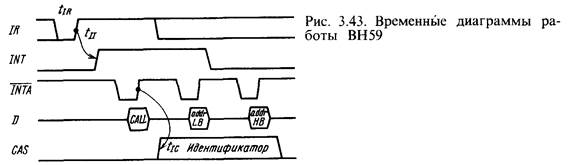

' Каскадное соединение нескольких БИС типа ВН59 (рис. 3.44) позволяет довести число приоритетных уровней до 64. В данном случае одна БИС действует

как ведущая (SP=1), а другие как ведомые (SP=0).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.