Лабораторная работа №12

Описание и моделирование регулярных (систолических) схем

Выполнил:

студент группы ЭC-31

Матылицкий И. В.

Цель работы: Изучить возможности языка VHDL и пакета ActiveHDL для описания и моделирования регулярных схем.

Выполнение работы

Задание:

1. Ввести имена входов и выходов схемы с использованием типа BIT_VECTOR.

2. Составить две VHDL-модели.

Способ 1.

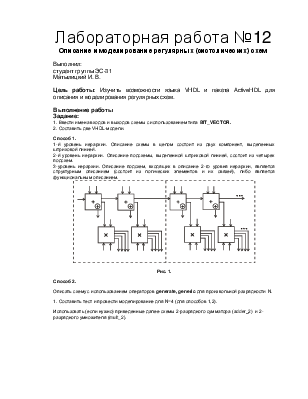

1-й уровень иерархии. Описание схемы в целом состоит из двух компонент, выделенных штриховой линией.

2-й уровень иерархии. Описание подсхемы, выделенной штриховой линией, состоит из четырех подсхем.

3-уровень иерархии. Описание подсхем, входящих в описание 2-го уровня иерархии, является структурным описанием (состоит из логических элементов и их связей), либо является функциональным описанием.

Рис. 1.

Способ 2.

Описать схему с использованием операторов generate, generic для произвольной разрядности N.

1. Составить тест и провести моделирование для N=4 (для способов 1,2).

Использовать (если нужно) приведенные далее схемы 2-разрядного сумматора (adder_2) и 2-разрядного умножителя (mult_2).

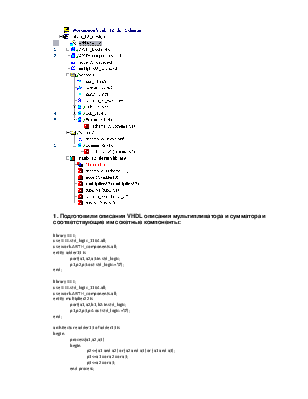

1. Подготовили описания VHDLописания мультипливатора и сумматора и соответствующие им сокетные компоненты:

library IEEE;

use IEEE.std_logic_1164.all;

use work.ARITH_components.all;

entity adder13 is

port(a1,a2,a3:in std_logic;

p1,p2,p3:out std_logic:='0');

end;

library IEEE;

use IEEE.std_logic_1164.all;

use work.ARITH_components.all;

entity multiplier22 is

port(a1,a2,b1,b2:in std_logic;

p1,p2,p3,p4:out std_logic:='0');

end;

architecture adder13 of adder13 is

begin

process(a1,a2,a3)

begin

p2<=(a1 and a2) or (a2 and a3) or (a1 and a3);

p1<=a1 xor a2 xor a3;

p3<=a2 xor a3;

end process;

end;

architecture multiplier22 of multiplier22 is

begin

process (a1,a2,b1,b2)

variable rank1,rank21,rank22,rank3:std_logic;

variable c2,c3:std_logic;

begin

rank1:=a1 and b1;

rank21:=a2 and b1;

rank22:=a1 and b2;

rank3:=a2 and b2;

c2:=rank21 and rank22;

c3:=c2 and rank3;

p1<=rank1;

p2<=rank21 xor rank22;

p3<=rank3 xor c2;

p4<=c3;

end process;

end;

Adder:

Multiplier:

library IEEE;

use IEEE.std_logic_1164.all;

package ARITH_components is

component adder13

port(a1,a2,a3:in std_logic;

p1,p2,p3:out std_logic:='0');

end component;

component multiplier22

port(a1,a2,b1,b2:in std_logic;

p1,p2,p3,p4:out std_logic:='0');

end component;

end;

package body ARITH_components is

end package body;

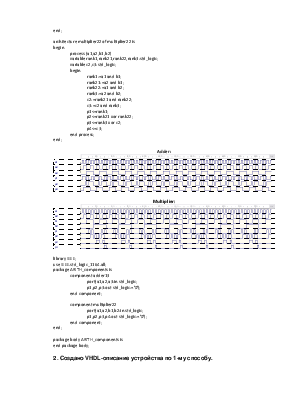

2. Создано VHDL-описание устройства по 1-му способу.

library IEEE;

use IEEE.std_logic_1164.all;

use work.arith_components.all;

entity sub2_v1 is

port(InV:in std_logic_vector(1 to 6);

OutV:out std_logic_vector(1 to 6));

end;

architecture sub2_v1 of sub2_v1 is

signal addout:std_logic;

begin

add:adder13

port map(a1=>InV(1),a2=>InV(2),a3=>InV(3),p1=>addout,p2=>OutV(1),p3=>OutV(2));

mult:multiplier22

port map(a1=>InV(4),a2=>InV(5),b1=>InV(6),b2=>addout,p1=>OutV(3),p2=>OutV(4),p3=>OutV(5),p4=>OutV(6));

end;

*********************************************************************************************

library IEEE;

use IEEE.std_logic_1164.all;

entity sub_v1 is

port(InV:in std_logic_vector(1 to 11);

OutV:out std_logic_vector(1 to 11));

end;

architecture sub_v1 of sub_v1 is

signal mes:std_logic;

component sub2_v1

port(InV:in std_logic_vector(1 to 6);

OutV:out std_logic_vector(1 to 6));

end component;

begin

amult1:sub2_v1

port map(InV(1 to 6)=>InV(1 to 6),OutV(1)=>mes,OutV(2 to 6)=>OutV(1 to 5));

amult2:sub2_v1

port map(InV(1)=>mes,InV(2 to 6)=>InV(7 to 11),OutV(1 to 6)=>OutV(6 to 11));

end;

*********************************************************************************************

library IEEE;

use IEEE.std_logic_1164.all;

entity schema_v1 is

port(InV:in std_logic_vector(1 to 21);

OutV:out std_logic_vector(1 to 21));

end;

architecture schema_v1 of schema_v1 is

signal mes:std_logic;

component sub_v1

port(InV:in std_logic_vector(1 to 11);

OutV:out std_logic_vector(1 to 11));

end component;

begin

subs1:sub_v1

port map(InV(1 to 11)=>InV(1 to 11),OutV(6)=>mes,

OutV(1 to 5)=>OutV(1 to 5),OutV(7 to 11)=>OutV(6 to 10));

subs2:sub_v1

port map(InV(1)=>mes,InV(2 to 11)=>InV(12 to 21),OutV(1 to 11)=>OutV(11 to 21));

end;

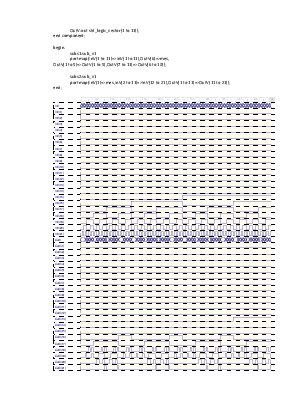

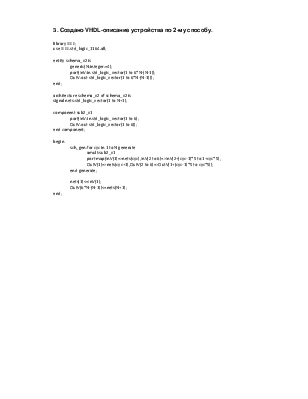

3. Создано VHDL-описание устройства по 2-му способу.

library IEEE;

use IEEE.std_logic_1164.all;

entity schema_v2 is

generic(N:integer:=4);

port(InV:in std_logic_vector(1 to 6*N-(N-1));

OutV:out std_logic_vector(1 to 6*N-(N-1)));

end;

architecture schema_v2 of schema_v2 is

signal nets:std_logic_vector(1 to N+1);

component sub2_v1

port(InV:in std_logic_vector(1 to 6);

OutV:out std_logic_vector(1 to 6));

end component;

begin

sch_gen:for cyc in 1 to N generate

amult:sub2_v1

port map(InV(1)=>nets(cyc),InV(2 to 6)=>InV(2+(cyc-1)*5 to 1+cyc*5),

OutV(1)=>nets(cyc+1),OutV(2 to 6)=>OutV(1+(cyc-1)*5 to cyc*5));

end generate;

nets(1)<=InV(1);

OutV(6*N-(N-1))<=nets(N+1);

end;

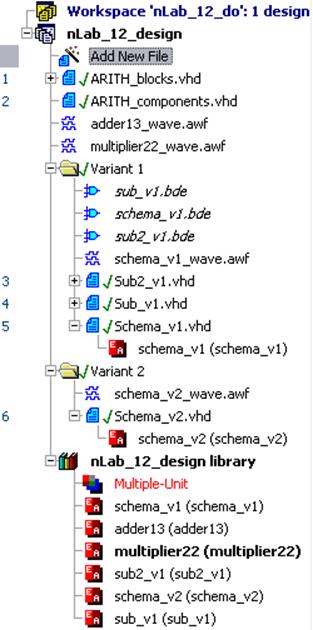

4. Созданы графические иерархические схемы.

Вывод: Были изучены возможности языка VHDL и пакета ActiveHDL для описания и моделирования регулярных схем (подстроечные константы, условная и циклическая генерация структуры).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.