5 Карта портов и карта настройки

Соединение VHDL-описаний осуществляется с помощью карт (mар).

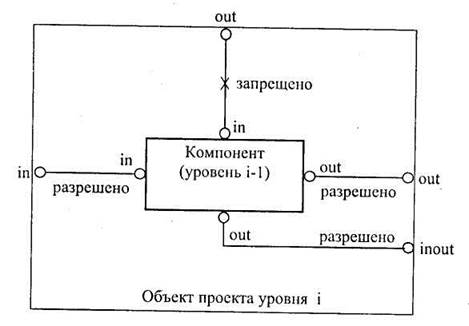

Для иерархического проекта порты низкоуровневых компонент (уровня i-1) могут быть отображены в порты высокоуровневого объекта (уровня i) сигналами с учетом следующих ограничений.

|

Рис. 5.1. Связи портов компонента с портами объекта |

Сигнал порта, имеющий режим (mode) in, может быть соединен с портом, имеющим режим in, inout, buffer (рис. 5.1).

На рис. 5.1 изображены только некоторые возможные соединения портов компонента с портами той подсхемы, в которую компонент входит.

Сигнал порта режима out может быть соединен с портом, имеющим режим out или inout, buffer. Сигнал порта режима inout, buffer может быть отображен (соединен) с портом, имеющим режим вида inout, buffer соответственно.

Сигнал порта режима linkage может быть соединен с сигналом порта любого режима. С точки зрения проектирования аппаратуры вид связи linkage не является естественным, данный тип связи более подходит для алгоритмических описаний.

Режим inout употребляется чаще всего для двунаправленных контактов, которые находятся снаружи кристалла СБИС. Для внутренних сигналов режим не указывается.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.