Лабораторная работа № 6

Анализ цифровых и цифро-аналоговых схем в системе PSpice

Выполнил : Косый А.М.

Цель работы: Изучить работу PSpice в качестве статического анализатора, изучить приёмы работы с программой при моделировании смешанных цифро-аналоговых схем.

Вариант №1

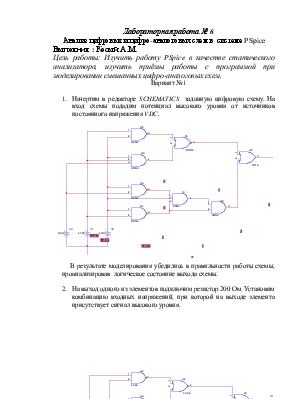

1. Начертим в редакторе SCHEMATICS заданную цифровую схему. На вход схемы подадим потенциал высокого уровня от источников постоянного напряжения VDC.

|

В результате моделирования убедились в правильности работы схемы, проанализировав логическое состояние выхода схемы.

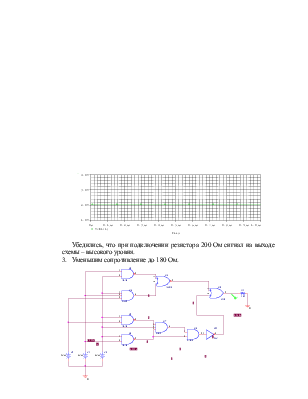

2. На выход одного из элементов подключим резистор 200 Ом. Установим комбинацию входных напряжений, при которой на выходе элемента присутствует сигнал высокого уровня.

|

|

Убедились, что при подключении резистора 200 Ом сигнал на выходе схемы – высокого уровня.

3. Уменьшим сопротивление до 180 Ом.

|

В результате моделирования получили, что при таком сопротивлении нагрузка для выходного каскада уже велика и на выходе схемы появляется неопределённое состояние.

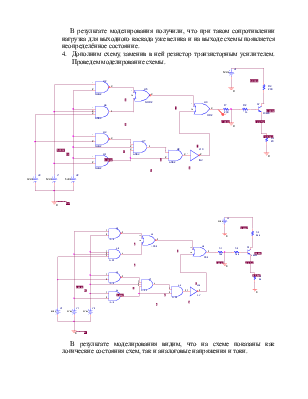

4. Дополним схему, заменив в ней резистор транзисторным усилителем. Проведем моделирование схемы.

|

|||

|

|||

В результате моделирования видим, что на схеме показаны как логические состояния схем, так и аналоговые напряжения и токи.

Файл Schematic1.out:

**** 05/24/04 13:00:32 ******** PSpice 9.2.2 (May 2001) ******* ID# 777164219

* Z:\Sapr\lab9\my2\Schematic1.sch

**** CIRCUIT DESCRIPTION

******************************************************************************

* Schematics Version 9.2.2

* Mon May 24 13:00:31 2004

** Analysis setup **

* From [PSPICE NETLIST] section of C:\Cadence\PSD_14.1\PSpice\PSpice.ini:

.lib "nom.lib"

.lib "C:\Cadence\PSD_14.1\PSpice\Library\opt.lib"

.lib "C:\Cadence\PSD_14.1\PSpice\Library\analog.lib"

.lib "nom.lib"

.INC "Schematic1.net"

**** INCLUDING Schematic1.net ****

* Schematics Netlist *

X_U9A $N_0001 $N_0002 $N_0003 $G_DPWR $G_DGND 7400 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U10A $N_0001 $N_0002 $N_0004 $G_DPWR $G_DGND 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U7A $N_0001 $N_0002 $N_0005 $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U15A $N_0001 $N_0003 $N_0006 $G_DPWR $G_DGND 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U16A $N_0006 $N_0007 $G_DPWR $G_DGND 7404 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U13A $N_0004 $N_0001 $N_0008 $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U11A $N_0008 $N_0007 $N_0009 $G_DPWR $G_DGND 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U14A $N_0010 $N_0001 $N_0005 $N_0011 $G_DPWR $G_DGND 7411 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U17A $N_0009 $N_0007 $N_0012 $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U12A $N_0001 $N_0010 $G_DPWR $G_DGND 7404 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U19A $N_0011 $N_0013 $N_0014 $G_DPWR $G_DGND 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U20A $N_0014 OUT $G_DPWR $G_DGND 7404 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

V_V2 $N_0001 0 5V

V_V1 $N_0002 0 5V

X_U21A $N_0012 $N_0013 $G_DPWR $G_DGND 7404 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

R_R7 $N_0013 0 180

**** RESUMING Schematic1.cir ****

.PROBE V(*) I(*) W(*) D(*) NOISE(*)

.END

**** Generated AtoD and DtoA Interfaces ****

*

* Analog/Digital interface for node $N_0001

*

* Moving X_U12A.U1:IN1 from analog node $N_0001 to new digital node $N_0001$AtoD

X$$N_0001_AtoD1

+ $N_0001

+ $N_0001$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U14A.U1:IN2 from analog node $N_0001 to new digital node $N_0001$AtoD2

X$$N_0001_AtoD2

+ $N_0001

+ $N_0001$AtoD2

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U13A.U1:IN2 from analog node $N_0001 to new digital node $N_0001$AtoD3

X$$N_0001_AtoD3

+ $N_0001

+ $N_0001$AtoD3

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U15A.U1:IN1 from analog node $N_0001 to new digital node $N_0001$AtoD4

X$$N_0001_AtoD4

+ $N_0001

+ $N_0001$AtoD4

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U7A.U1:IN1 from analog node $N_0001 to new digital node $N_0001$AtoD5

X$$N_0001_AtoD5

+ $N_0001

+ $N_0001$AtoD5

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U10A.U1:IN1 from analog node $N_0001 to new digital node $N_0001$AtoD6

X$$N_0001_AtoD6

+ $N_0001

+ $N_0001$AtoD6

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Moving X_U9A.U1:IN1 from analog node $N_0001 to new digital node $N_0001$AtoD7

X$$N_0001_AtoD7

+ $N_0001

+ $N_0001$AtoD7

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.