Подача на управляющие входы мультиплексора сигналов, соответствующих ky переменным, по которым раскладывается ФАЛ.

5. Подача на информационные входы мультиплексора сигналов, соответствующих значениям функций fi.

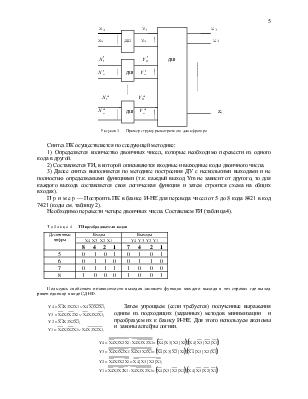

П р и м е р.

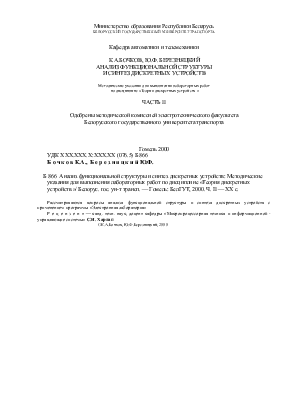

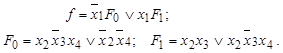

Построить на мультиплексорах с двумя управляющими входами схему, реализующую

ФАЛ ![]()

Разложим функцию по x1 и x2 и получим

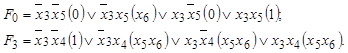

![]()

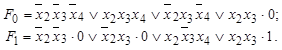

Для реализации ФАЛ ![]() и

и ![]() будем

осуществлять разложение F0 по х3

и х5, а F3 ¾ по х3 и х4:

будем

осуществлять разложение F0 по х3

и х5, а F3 ¾ по х3 и х4:

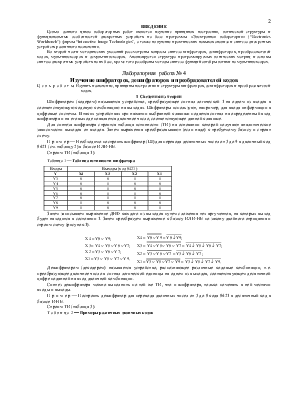

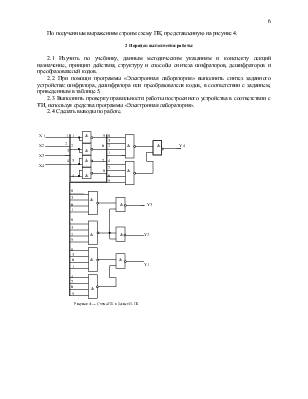

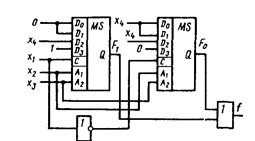

На основе полученных выражений и алгоритма строим схему (рисунок 2).

Рисунок 2 ¾ Схема реализации функции алгебры логики

на четырехвходовых мультиплексорах

Использование синхронизирующего входа МП. Наличие синхронизирующего входа позволяет расширить возможности реализации ФАЛ на мультиплексорах.

Алгоритм реализация ФАЛ k переменных с использованием двух мультиплексоровс синхронизирующими входами.

1. На писание заданной ФАЛ в ДНФ;

2. Разложение заданной ФАЛ по переменной с индексом i;

3. Нахождение выражения функций F0 и F1 переменных (k—1).

4. Реализация ФАЛ F0 и F1 на мультиплексорах с k—2 управляющими входами. Сигналы, соответствующие (k — 2) переменным, подать параллельно на управляющие входы обоих мультиплексоров.

5. Подача сигнала, соответствующего переменной с индексом i на стробирующий вход первого мультиплексора, реализующего ФАЛ F1, и через инвертор — на стробирующий вход второго мультиплексора, реализующего ФАЛ F0.

6. Объединение прямых выходов мультиплексоров, используя элемент ИЛИ.

Рассмотрим это на примере.

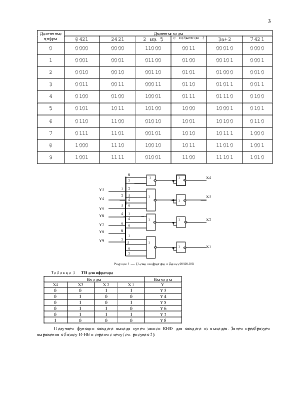

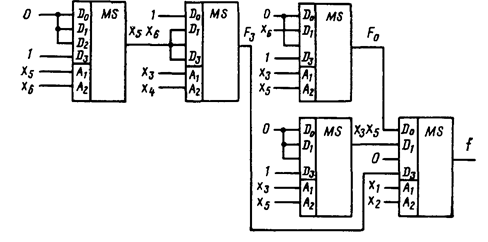

П р и м е р. Построить схему на мультиплексорах с двумя управляющими и

стробирующими входами для ФАЛ четырех переменных ![]()

Разложим ФАЛ по переменной x1:

Величины F0 и F1 являются функциями трех переменных и могут быть реализованы на мультиплексорах с двумя управляющими входами на основании вышеприведенного алгоритма. Разложим функции F0 и F1 по x2 и x3:

Если на синхронизирующие входы мультиплексоров, реализующих F0 и F1, подать сигналы,

соответствующие переменной, дизъюнкция выходных функции на прямых выходах обоих

мультиплексоров реализует заданную ФАЛ (рисунок 3).

Если на синхронизирующие входы мультиплексоров, реализующих F0 и F1, подать сигналы,

соответствующие переменной, дизъюнкция выходных функции на прямых выходах обоих

мультиплексоров реализует заданную ФАЛ (рисунок 3).

Рисунок 3 ¾ Схема реализация функции алгебры логики на мультиплексорах с синхронизирующим входом

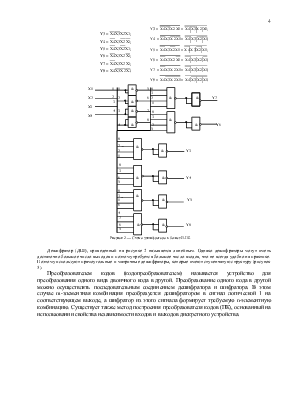

Мультиплексоры с числом управляющих входов k у могут быть использованы совместно с элементами некоторого базиса для реализации ФАЛ k переменных. В этом случае на информационные входы подаются функции k — ky переменных, сформированные элементами выбранного базиса.

Следует учитывать, что, синтезируя дискретное устройство (реализуя ФАЛ) с использованием мультиплексоров, необходимо также построить вариант схемы без использования мультиплексора. Затем сравнить оба варианта, и определить, какой из них лучше по числу используемых корпусов интегральных микросхем.

2.1 Изучить теоретический материал по данным методическим указаниям и учебнику.

2.2 В соответствии с заданным вариантом (таблица 1), осуществить разложение и построить схему реализации ФАЛ на мультиплексорах.

2.3 Построить таблицу истинности заданной ФАЛ по исходной формуле и проверить правильность функционирования полученной схемы на мультиплексорах путем сверки выходных значений функций по таблице истинности.

2.4 Построить исходную ФАЛ обычным способом (без использования мультиплексоров) и сравнить варианты реализации.

2.4 Сделать выводы по сравнению вариантов реализации ФАЛ с использованием мультиплексоров и без их использования.

Наименование и цель работы, таблица истинности, полученная по исходной ФАЛ и таблица истинности, полученная при практической проверке схемы, схема

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.