6 Синтез устройства вычитания

Двоичные вычитатели выполняют арифметическую операцию вычитания двоичных чисел и используются преимущественно в арифметико-логических устройствах современных ЭВМ и цифровых фильтрах.

Устройство вычитания – обратная операция сложению по модулю два. В данном курсовом проекте будем выполнять вычитание кода счетчика импульсов СТ из регистра RG.

Таблица истинности одноразрядного вычитателя параллельного действия для i-го разряда содержит три двоичных входа: аi и bi – вычитаемые разряды и zi–1 – заем из i разряда в i-1-й (таблица 6.1).

Таблица 6.1 – Таблица истинности одноразрядного вычитателя

|

Входы |

Выходы |

|||

|

ai |

bi |

zi-1 |

ri |

zi |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Исходя из таблицы истинности, запишем функции выходов ri и zi:

![]()

![]()

Минимизируем полученные функции с помощью карт Карно:

Функция ri:

функция ![]() не упрощается.

не упрощается.

Функция zi:

![]()

![]()

Реализуем устройство вычитания на мультиплексорах [2].

Разложим

![]() по

по ![]() и

и ![]() :

:

![]() ;

;

![]()

![]()

![]()

![]()

Разложим ![]() по

по ![]() и

и ![]() :

:

![]() ;

;

![]()

![]()

![]()

![]()

В этом случае ![]() .

.

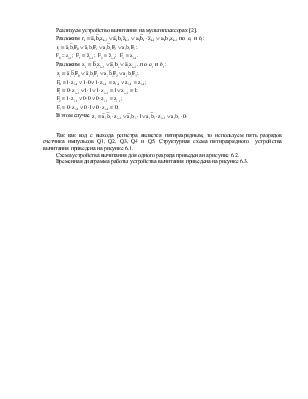

Так как код с выхода регистра является пятиразрядным, то используем пять разрядов счетчика импульсов Q1, Q2, Q3, Q4 и Q5. Структурная схема пятиразрядного устройства вычитания приведена на рисунке 6.1.

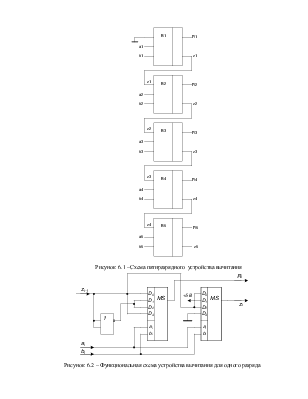

Схема устройства вычитания для одного разряда приведена на рисунке 6.2.

Временная диаграмма работы устройства вычитания приведена на рисунке 6.3.

Рисунок 6.1 –Схема пятиразрядного устройства вычитания

Рисунок 6.2 – Функциональная схема устройства вычитания для одного разряда

Рисунок 6.3 – Временная диаграмма работы устройства вычитания

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.