Для таблицы

данных отведена область ПЗУ, начиная с адреса ![]() . Для хранения двухбайтовых чисел используются две

соседние ячейки памяти с адресами

. Для хранения двухбайтовых чисел используются две

соседние ячейки памяти с адресами ![]() и

и ![]() . Подпрограмма TAB определяет адрес младшего байта

данных и читает его из ПЗУ. Для определения адреса

. Подпрограмма TAB определяет адрес младшего байта

данных и читает его из ПЗУ. Для определения адреса ![]() по коду нажатой клавиши к начальному адресу

по коду нажатой клавиши к начальному адресу ![]() прибавляется удвоенный код клавиши. Таким образом, по

коду клавиши, например, с номером

прибавляется удвоенный код клавиши. Таким образом, по

коду клавиши, например, с номером ![]() , задающей в соответствии с рисунком

20 скорость

, задающей в соответствии с рисунком

20 скорость ![]() , определяются адреса двух ячеек

памяти

, определяются адреса двух ячеек

памяти ![]() , где хранятся соответственно младший

и старший байты числа

, где хранятся соответственно младший

и старший байты числа ![]() . При выполнении команды OUT 10h по сигналам

. При выполнении команды OUT 10h по сигналам ![]() и

и ![]() вырабатывается сигнал

вырабатывается сигнал ![]() (рисунок 21), перепадом с 0 на 1 которого в триггер

знака

(рисунок 21), перепадом с 0 на 1 которого в триггер

знака ![]() записывается значение разряда

записывается значение разряда ![]() .

.

При работе имитатора CPU обращается к внешним устройствам к двум схемам памяти (ПЗУ и ОЗУ):

· ПЗУ 573РФ2

объемом ![]() бит (для хранения программного

обеспечения и таблицы данных);

бит (для хранения программного

обеспечения и таблицы данных);

· ОЗУ 537РУ10

объемом ![]() бит (для стека и хранения данных).

бит (для стека и хранения данных).

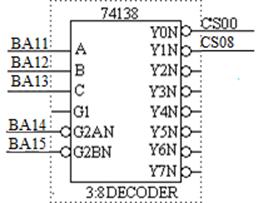

Поэтому

необходимо использовать два дешифратора адресов – адресов схем памяти и адресов

внешних устройств. Дешифратор адресов схем памяти выполнен на МЭ 74138.

Назначение выходных сигналов дешифратора, значения начальных ![]() и конечных

и конечных ![]() адресов представлены в таблице 5.

адресов представлены в таблице 5.

|

Таблица 5 Адреса схем памяти |

||||||

|

Адрес |

|

|

|

|

||

|

ПЗУ

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ОЗУ

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Дешифратор адресов изображён на рисунке 21.

Рис.21. Дешифратор адресов схем памяти.

При построении схемы на макроэлементах, в состав которой входят два 16-разрядных счетчика, число внешних устройств увеличивается до восьми:

· регистр

младшего байта данных в делителе на ![]()

· регистр

старшего байта данных в делителе на ![]()

· регистр

младшего байта данных в делителе на ![]()

· регистр

старшего байта данных в делителе на ![]()

· триггер знака ![]() ;

;

· контроллер клавиатуры;

· дисплей.

Для создания

схемы дешифратора адресов внешних устройств, обязанной обеспечить заданный

адрес ![]() , выбираем значения разрешающих

адресных сигналов

, выбираем значения разрешающих

адресных сигналов ![]() , а на адресные входы С, B и A подаем сигналы

, а на адресные входы С, B и A подаем сигналы ![]() (сигналы

(сигналы ![]() не поступают на схему). Таблица 6

показывает адреса и названия внешних устройств, селектируемых дешифратором. На рисунке

22 показана схема дешифратора адресов внешних устройств.

не поступают на схему). Таблица 6

показывает адреса и названия внешних устройств, селектируемых дешифратором. На рисунке

22 показана схема дешифратора адресов внешних устройств.

|

Таблица 6 Адресация внешних устройств |

||

|

Сигнал |

Адрес |

Селектируемое устройство |

|

|

|

Триггер |

|

|

|

Регистр

старшего байта счетчика |

|

|

|

Регистр

младшего байта счетчика |

|

|

|

Регистр

старшего байта счетчика |

|

|

|

Регистр

младшего байта счетчика |

|

|

|

Клавиатура |

|

|

|

Дисплей |

|

|

|

Рис.22. Дешифратор адресов внешних устройств. |

Принципиальная

схема памяти изображена на рисунке 23: 573РФ2 – ПЗУ объемом ![]() бит, 537РУ10 – ОЗУ объемом

бит, 537РУ10 – ОЗУ объемом ![]() бит. Выбор ПЗУ производится

значением сигнала

бит. Выбор ПЗУ производится

значением сигнала ![]() , а выбор ОЗУ – значением сигнала

, а выбор ОЗУ – значением сигнала ![]() . Адресные сигналы

. Адресные сигналы ![]() подаются непосредственно на адресные

входы БИС и обеспечивают адресацию 2K 8-разрядных ячеек памяти от адреса 0000h

до адреса 07FFh для ПЗУ, и от адреса 0800h до адреса 0FFFh для ОЗУ (см. табл. 5).

Чтение ПЗУ и ОЗУ производится значением сигнала

подаются непосредственно на адресные

входы БИС и обеспечивают адресацию 2K 8-разрядных ячеек памяти от адреса 0000h

до адреса 07FFh для ПЗУ, и от адреса 0800h до адреса 0FFFh для ОЗУ (см. табл. 5).

Чтение ПЗУ и ОЗУ производится значением сигнала ![]() , а запись данных в ОЗУ – сигналом

, а запись данных в ОЗУ – сигналом ![]() . Обычно под стек отводится часть

ОЗУ, занимающая старшие адреса, поэтому инициализацию стека следует производить

командой LXI SP,1000h.

. Обычно под стек отводится часть

ОЗУ, занимающая старшие адреса, поэтому инициализацию стека следует производить

командой LXI SP,1000h.

Данные ![]() должны подаваться с системной шины

данных

должны подаваться с системной шины

данных ![]() через приемопередатчик. При

обращении CPU к другим устройствам (пульт управления, плата расширения системы)

этот приемопередатчик должен быть выключен, поэтому следует правильно

определить управляющий приемопередатчиком сигнал

через приемопередатчик. При

обращении CPU к другим устройствам (пульт управления, плата расширения системы)

этот приемопередатчик должен быть выключен, поэтому следует правильно

определить управляющий приемопередатчиком сигнал ![]() .

.

|

|

|

Рис.23. Схема подключения памяти. |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.