![]() кОм;

кОм;

![]() кОм.

кОм.

Выбираем

Выбираем ![]() кОм. Величина

кОм. Величина ![]() определяется по тем же формулам

при р=1 и учете входных токов мультиплексора. Расчет показывает возможность выбора

определяется по тем же формулам

при р=1 и учете входных токов мультиплексора. Расчет показывает возможность выбора ![]() .

.

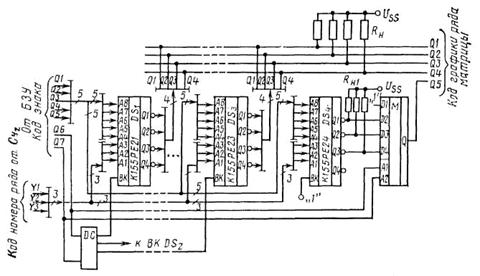

Рис. 3.5. Структурная схема знакогенератора на БИС ПЗУ 155РЕ21-РЕ24

Задание 3.4.

Используя БИС ППЗУ Нк KI55 PE3 с информационной емкостью ![]() закодировать

графику десяти цифр 0−9. Код обмена информацией − двоично-десятичный с весами

8−4−2−1. Матрица знака 5×7.

закодировать

графику десяти цифр 0−9. Код обмена информацией − двоично-десятичный с весами

8−4−2−1. Матрица знака 5×7.

В соответствии с (3.24) и (3.28) ![]() ,

,

![]() определим величину

определим величину ![]() .

.

Исходную организацию ППЗУ Нк представляем в

соответствии с (3.29) ![]() , как 4×8×8, т. е. с

помощью одной микросхемы можно закодировать четыре цифры. Общее количество БИС Нк

определим в соответствии с (3.30):

, как 4×8×8, т. е. с

помощью одной микросхемы можно закодировать четыре цифры. Общее количество БИС Нк

определим в соответствии с (3.30): ![]() ;

; ![]() .

.

Для выбора информации о графике одной из четырех цифр, закодированной в одной ИМС, используем два младших разряда двоично-десятичного кода цифры, подавая их па два старших адресных разряда ПЗУ Нк А5; А4.

Три остальных адресных разряда A3; А2; А1 используются

для вертикальной развертки знака, для чего на них подается код номера

ряда матрицы ![]() ;

; ![]() ;

; ![]() . Выбор

одной из трех БИС по входам ВK через дешифратор осуществляется двумя старшими

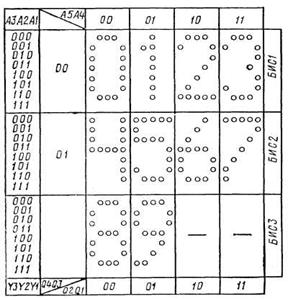

разрядами кода знака Q4Q5. В соответствии со сказанным на рис. 3.6 показано

размещение информации о графике цифр в ПЗУ.

. Выбор

одной из трех БИС по входам ВK через дешифратор осуществляется двумя старшими

разрядами кода знака Q4Q5. В соответствии со сказанным на рис. 3.6 показано

размещение информации о графике цифр в ПЗУ.

|

Рис. 3.6. Размещение информации о графике цифр в ППЗУ

Задание 3.5.

Исправить содержимое ячеек памяти с адресами 128–36 ППЗУ с

информационной емкостью ![]() . БИС ППЗУ имеют выходы с тремя устойчивыми состояниями. В соответствии

с заданием число ячеек памяти, подлежащих исправлению, равно 9, разрядность

. БИС ППЗУ имеют выходы с тремя устойчивыми состояниями. В соответствии

с заданием число ячеек памяти, подлежащих исправлению, равно 9, разрядность ![]() .

Следовательно, согласно формуле

(3.31)

.

Следовательно, согласно формуле

(3.31) ![]() ,

, ![]() . Выбираем БИС ПЗУ Нк с организацией

16×4.

. Выбираем БИС ПЗУ Нк с организацией

16×4.

Рассматриваем коды адресов (128–136) ячеек памяти, подлежащих исправлению, которые сведем в табл. 3.3.

Из таблицы видим, что переменное значение имеют четыре младших

разряда А4–А1; следовательно, ![]() , а вся область, где находятся ячейки

памяти, содержимое которых подлежит исправлению, определяется старшими разрядами

A8–A1, =1000. В соответствии с формулами (3.32)

и (3.33)

, а вся область, где находятся ячейки

памяти, содержимое которых подлежит исправлению, определяется старшими разрядами

A8–A1, =1000. В соответствии с формулами (3.32)

и (3.33) ![]() ,

, ![]() ;

; ![]() .

.

Схема ПЗУ с внесенными исправлениями содержимого основной БИС ППЗУ представлена па рис. 3.7. С помощью микросхемы DD1 по входу выбора микросхемы ВK выбирается ПЗУ адресов исправляемых ячеек памяти DS2. При адресации к исправляемой ячейке памяти сигналом с выхода Q5 DS2 осуществляется запрет работы основной схемы ПЗУ DS1 и разрешается работа схемы DS3, где хранится исправленное значение кода.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.