Билет №16

Элементы и узлы ПЭВМ: Дешифраторы, шифраторы, мультиплексоры.

Дешифраторы

Дешифратором (избирательной схемой) называется ком-бинационная логическая схема без элементов памяти, в кото-рой определенная комбинация входных сигналов вызывает по-явление сигнала только на одной соответствующей выходной шине.

Пусть некоторая совокупность входных сигналов

(цифро-вых кодов) выражается наборами ![]() двоичных

переменных

двоичных

переменных ![]() . С помощью

. С помощью ![]() переменных

возможно образовать

переменных

возможно образовать ![]() различных кодов и, если

требуется однозначно определить каждый из наборов переменных (кодов),

дешифратор должен иметь

различных кодов и, если

требуется однозначно определить каждый из наборов переменных (кодов),

дешифратор должен иметь ![]() выходов. Такой

дешифратор называется полным.

выходов. Такой

дешифратор называется полным.

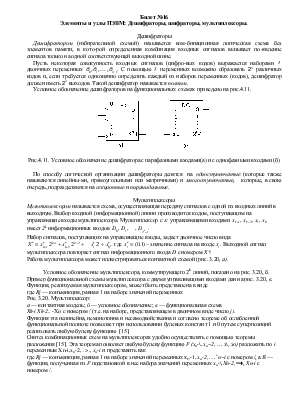

Условное обозначение дешифраторов на функциональных схемах приведено на рис.4.11.

Рис.4.11. Условное обозначение дешифратора с парафазными входами(а) и с однофазными входами (б)

По способу логической организации дешифраторы делятся на одноступенчатые (которые также называются линейны-ми, прямоугольными или матричными) и многоступенчатые, которые, в свою очередь, подразделяются на секционные и пирамидальные.

Мультиплексоры

Мультиплексором называется

схема, осуществляющая передачу сигналов с одной из входных линий в выходную.

Выбор входной (информационной) линии производится кодом, поступающим на

управляющие входы мультиплексора. Мультиплексор с ![]() управляющими

входами

управляющими

входами ![]() имеет 2k информационных входов

имеет 2k информационных входов ![]()

Набор сигналов, поступающих на управляющие входы, задает двоичное число вида

![]() где

где ![]() –

значение сигнала на входе

–

значение сигнала на входе![]() . Выходной сигнал

мультиплексора повторяет сигнал информационного входа D с номером X*.

. Выходной сигнал

мультиплексора повторяет сигнал информационного входа D с номером X*.

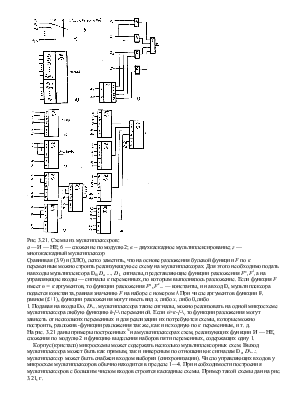

Работа мультиплексора может иллюстрироваться контактной схемой (рис. 3.20, а).

Условное обозначение мультиплексора, коммутирующего 2k линий, показано на рис. 3.20, б.

Пример функциональной схемы мультиплексора с двумя управляющими входами дан на рис. 3.20, в.

Функция, реализуемая мультиплексором, может быть представлена в виде

где Rj — конъюнкция, равная 1 на наборе значений переменных

Рис. 3.20. Мультиплексор:

а — контактная модель; б — условное обозначение; в — функциональная схема

Xk-i Xk-2.. -Хо с номером / (т.е. на наборе, представляющем в двоичном виде число j).

Функция эта нелинейна, немонотонна и несамодвойственна и согласно теореме об ослабленной функциональной полноте позволяет при использовании булевых констант 1 и 0 путем суперпозиций реализовать любую булеву функцию [15].

Синтез комбинационных схем на мультиплексорах удобно осуществлять с помощью теоремы разложения [15]. Эта теорема позволяет любую булеву функцию F (хп-\, хп~2, ..., х\у хо) разложить по i переменным Xn-i,xn-2, . >., xn-i и представить как

где Rj — конъюнкция, равная 1 на наборе значений переменных х„-1, хп-2, ..., xn~i с номером /, а Я — функция, полученная из F подстановкой в нее набора значений переменных хп-\,Хп-2, ••♦, Xn-i с номером /.

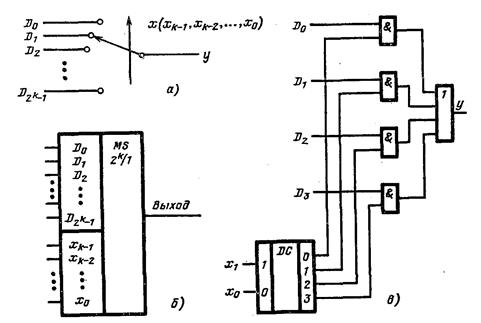

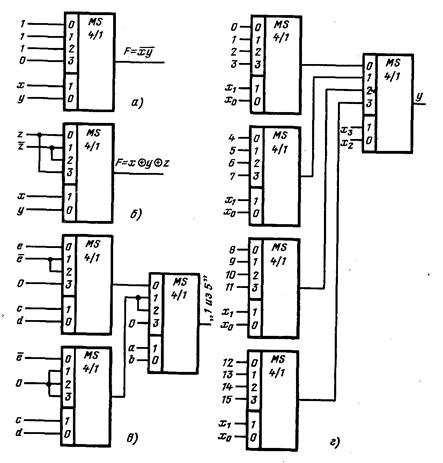

Рис. 3.21. Схемы из мультиплексоров:

а — И — НЕ; 6 — сложение по модулю 2; в ~ двухкаскадное мультиплексирование; г — многокаскадный мультиплексор

Сравнивая (3.9) и (ЗЛО), легко заметить, что на основе разложения булевой функции F по к переменным можно строить реализующую ее схему на мультиплексорах. Для этого необходимо подать на входы мультиплексора D0) Du ..., D k сигналы, представляющие функции разложения F°t Fl, а на управляющие входы — сигналы к переменных, по которым выполнялось разложение. Если функция F имеет п = к аргументов, то функции разложения F°, Fх... — константы, и на вход D, мультиплексора подается константа, равная значению F на наборе с номером /\ При числе аргументов функции F, равном (£+1), функции разложения могут иметь вид х, либо х, либо 0, либо

1. Подавая на входы Do, D\... мультиплексора такие сигналы, можно реализовать на одной микросхеме мультиплексора любую функцию k-{-\ переменной. Если п>к-{-\у то функции разложения могут зависеть от нескольких переменных и для реализации их потребуются схемы, которые можно построить, разложив -функции разложения так же, как и исходную по к переменным, и т. д.

На рис. 3.21 даны примеры построенных %на мультиплексорах схем, реализующих функции И — НЕ, сложения по модулю 2 и функцию выделения наборов пяти переменных, содержащих одну 1.

Корпус (кристалл) микросхемы может содержать несколько мультиплексорных схем. Выход мультиплексора может быть как прямым, так и инверсным по отношению к сигналам Do, D\...; мультиплексор может быть снабжен входом выборки (синхронизации). Число управляющих входов у микросхем мультиплексоров обычно находится в пределе 1—4. При необходимости построения мультиплексоров с большим числом входов строятся каскадные схемы. Пример такой схемы дан на рис. 3.21, г.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.