Изучение способов задания логических функций.

Изучение методов приведения логической функции к заданному базису.

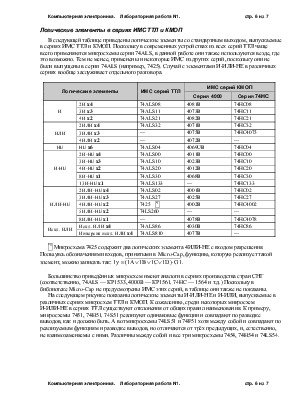

Ознакомление с номенклатурой логических элементов в сериях ИМС ТТЛ и КМОП.

Приобретение навыков построения и моделирования цифровых схем в программе Micro-Cap.

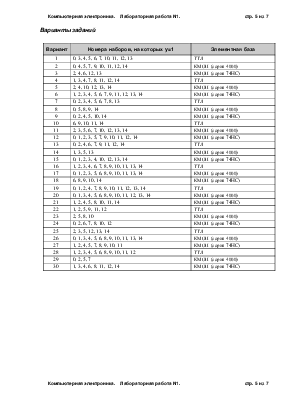

Логическая функция y = f(x3, x2, x1, x0) задана следующим образом: перечислены номера наборов, на которых она принимает значение 1. Номер набора — это десятичное представление двоичного числа x3x2x1x0 (например, x3=1, x2=0, x1=1, x0=0 — это набор 10).

1. Построить таблицу истинности функции.

2. Занести значения функции в карту Карно.

3. На основании карты Карно представить функцию

четырьмя способами: МДНФ для ![]() , МДНФ для

, МДНФ для ![]() , МКНФ для

, МКНФ для ![]() , МКНФ

для

, МКНФ

для ![]() .

.

4. Привести МДНФ для ![]() и для

и для ![]() к базису И‑НЕ. Выбрать оптимальный вариант

для построения логической схемы: непосредственно

к базису И‑НЕ. Выбрать оптимальный вариант

для построения логической схемы: непосредственно ![]() , или же

, или же

![]() и дополнительный элемент И‑НЕ в качестве

инвертора. Построить логическую схему, используя конкретные логические элементы

И‑НЕ из серий ИМС ТТЛ или КМОП в соответствии с вариантом задания.

и дополнительный элемент И‑НЕ в качестве

инвертора. Построить логическую схему, используя конкретные логические элементы

И‑НЕ из серий ИМС ТТЛ или КМОП в соответствии с вариантом задания.

5. Привести МКНФ для ![]() и для

и для ![]() к базису ИЛИ‑НЕ. Выбрать оптимальный

вариант для построения логической схемы: непосредственно

к базису ИЛИ‑НЕ. Выбрать оптимальный

вариант для построения логической схемы: непосредственно ![]() , или же

, или же ![]() и

дополнительный элемент ИЛИ‑НЕ в качестве инвертора. Построить логическую схему,

используя конкретные логические элементы ИЛИ‑НЕ из серий ИМС ТТЛ или КМОП в

соответствии с вариантом задания.

и

дополнительный элемент ИЛИ‑НЕ в качестве инвертора. Построить логическую схему,

используя конкретные логические элементы ИЛИ‑НЕ из серий ИМС ТТЛ или КМОП в

соответствии с вариантом задания.

6. Преобразовать (упростить) функцию для реализации её при помощи как можно меньшего числа логических элементов, выбрав из четырёх вариантов представления функции оптимальный и ориентируясь на конкретные логические элементы из серий ИМС ТТЛ или КМОП в соответствии с вариантом задания (нередко схему можно упростить, используя такие элементы, как исключающее ИЛИ, инверсия исключающего ИЛИ и различные элементы И‑ИЛИ‑НЕ). Построить логическую схему.

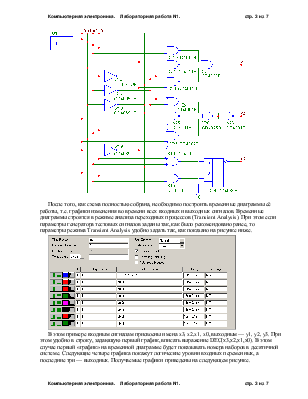

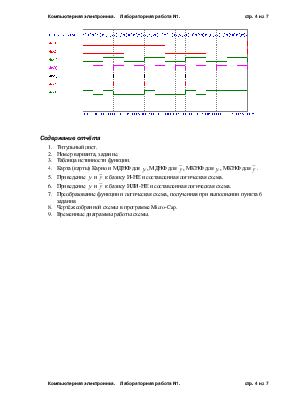

7. Собрать три полученных схемы в программе Micro-Cap. Подключить генератор тестовых сигналов и задать параметры генерируемых сигналов. В режиме Transient Analysis построить временные диаграммы работы всех трёх схем на одном графике. Убедиться, что они соответствуют таблице истинности на всех комбинациях входных сигналов для всех трёх схем.

Вопросы, связанные с построением таблицы истинности, построением карты Карно, приведением функции к определённому базису, преобразованием/упрощением и построением логической схемы были подробно рассмотрены в курсе лекций. Остановимся на тех вопросах, которые относятся к работе с реальными логическими элементами и непосредственно к реализации проекта в программе Micro-Cap.

В каждом варианте задания задана элементная база (микросхемы серий ТТЛ, микросхемы КМОП серии 4000, микросхемы КМОП серии 74HC), на которой необходимо реализовать схему. Для размещения на схеме цифровых ИМС используется меню Component – Digital Library; в нём все микросхемы размещены в нескольких подменю. ИМС серии 4000 размещены в подменю CD4000.

К сожалению, не каждый логический элемент, который было бы удобно применить для реализации функции, существует в виде микросхемы. Например, пусть для реализации схемы на ИМС ТТЛ необходим элемент 9И‑НЕ. Как видно из таблицы, микросхем, содержащих именно такой элемент, нет. Зато есть ИМС 74ALS133, представляющая собой элемент 13И‑НЕ. В этом случае используем этот элемент с тринадцатью входами как девятивходовый, подключив соответствующим образом четыре неиспользованных входа.

Ещё один пример. Пусть для реализации схемы на ИМС ТТЛ необходим элемент 4ИЛИ. Как видно, именно таких элементов в сериях ИМС ТТЛ также нет. В этом случае реализуем четырёхвходовый элемент ИЛИ на трёх двухвходовых.

Иногда необходимо подать на вход логического элемента постоянный логический уровень 0 или 1. В Micro-Cap для этого используется источник фиксированных логических уровней (Component - Digital Primitives - Stimulus Generators - Fixed Digital). После размещения его на схеме открывается окно задания атрибутов, в котором нужно атрибуту VALUE присвоить, соответственно, значение 0 или 1.

В качестве источника входных сигналов, т.е. значений входных переменных, используется генератор тестовых сигналов имеющий четыре выхода (Component - Digital Primitives - Stimulus Generators - Stim4). После размещения его на схеме открывается окно задания атрибутов, в котором необходимо задать закон изменения во времени логических уровней на выходах генератора. В данной работе удобно использовать такую последовательность значений входных переменных, в которой номера наборов последовательно возрастают от 0000 до 1111, а длительность каждого состояния — 1 мс. Для получения такой последовательности необходимо задать параметры генератора (текстовое поле .define в нижнем поле ввода) как показано на следующем рисунке.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.