Рассмотренное преобразование адреса называется страничным.

Механизм страничной адресации позволяет обеспечить гарантированную защиту данных в ОЗУ от несанкционированного доступа со стороны приложений. Это достигается наличием в ДП двух «комплектов» регистров: для системного и пользовательского режимов. Адресуются эти регистры, наряду с регистрами других внешних устройств (ВУ), через особую страницу физического адресного пространства.

Страничное отображение для пользовательского режима настраивается так, чтобы страницы внешних устройств и операционной системы были недоступны. При этом обратиться к ОС прикладная программа может только через вызов прерывания. При прерывании происходит переключение в системный режим, что меняет отображение страниц, делая доступным код ОС. Однако одновременно с этим прикладная программа обязательно теряет управление, что исключает ей возможность доступа к коду и данным ОС.

1.4.2. Средства поддержки многозадачности в архитектуре IA32.

Для рассмотрения способа управления памятью необходимо привести основные регистры процессора. В процессорах архитектуры IA32 (32-разрядная архитектура Intel, которую реализуют процессоры, начиная с i386) имеются следующие регистры.

Регистры общего назначения (РОН): EAX, EBX, ECX, EDX, EGI, EDI, EBP, ESP. Первые четыре используются для хранения данных при вычислениях, последние – для инкрементных операций.

Сегментные регистры: CS, SS, DS, ES, FS, GS. Используются для адресации.

Указатель на текущую инструкцию EIP и регистр флагов EFLAGS.

Перечисленные регистры относятся к основным. Следующие регистры являются системными, непосредственный доступ к ним разрешен только при наивысшем уровне привилегий:

CR0 — регистр состояния, определяет режим работы процессора;

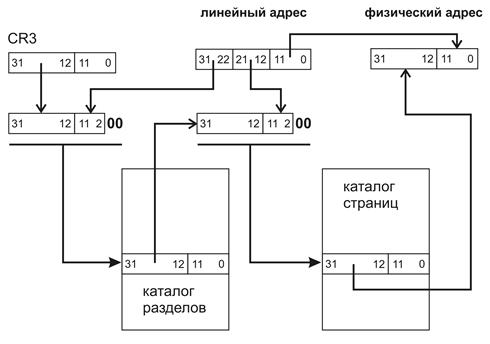

CR3 — база каталога страниц;

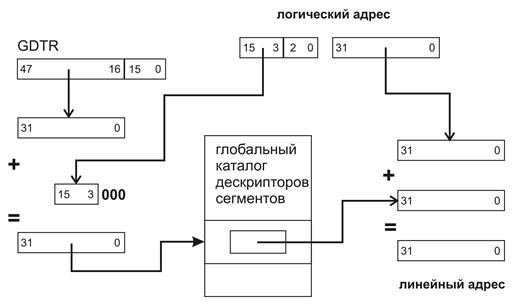

GDTR — указатель на глобальную таблицу дескрипторов сегментов;

TR — селектор сегмента статуса задачи.

Сегментные регистры и TR имеют 16 разрядов, GDTR — 48 разрядов, остальные регистры 32-разрядны.

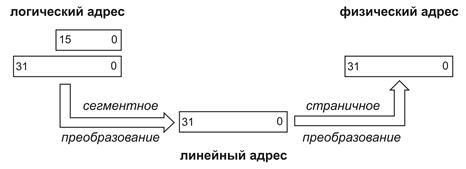

Преобразование адреса в IA32 осуществляется (см. Рис. 7) в два этапа: сначала логический адрес, состоящий из 32-разрядного относительного адреса и 16-разрядного значения сегментного регистра преобразуется (эта операция называется сегментным преобразованием) в 32-разрядный линейный адрес, который затем страничным преобразованием заменяется 32-разрядным физическим адресом.

Рис. 7. Общая схема преобразования адреса в IA32.

Указанные преобразования различаются в разных режимах работы процессора: защищенном, виртуального-86 и реальном.

Рис. 8. Страничное преобразование в IA32.

Процесс страничного преобразования приведен на рис. 8. Его принцип такой же, как и в PDP–11, но добавлен один уровень, а именно, страницы сгруппированы по разделам. Это объясняется тем, что объем памяти может быть значительным, и число страниц может достигать 1048576. Кроме того, если регистр диспетчера памяти содержал только адрес страницы, то в каталогах страниц и разделов хранятся дескрипторы страниц, которые помимо адреса содержат дополнительные атрибуты, в частности бит действительности. Последний позволяет указать, что для данной страницы физическая память не выделена, и обращение к ней невозможно. При попытке обращения к такой странице возникает исключение. Это позволяет реализовать механизм виртуальной памяти, когда ОС выделяет память приложению не заранее, а по мере необходимости, причем возможно повторное использование одних и тех же областей физической памяти.

Защищенный режим является основным для архитектуры IA32. В нем сегментное и страничное преобразование производятся полностью, а уровень привилегий может быть задан любой из четырех. Сегментное преобразование является более гибким, чем страничное, поскольку сегмент в отличие от страницы может иметь произвольное расположение в адресном пространстве. Сегментный регистр содержит индекс сегмента.

Рис. 9. Сегментное преобразование в IA32.

На рис. 9 приведена схема сегментного преобразования для защищенного режима в простейшем случае (с использованием глобальной таблицы дескрипторов).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.