Далее рассмотрим каждый элемент в отдельности.

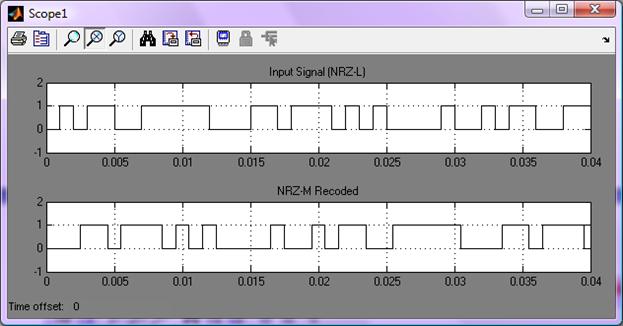

Работа блока PN Sequence Generator, основана на использовании сдвиговых регистров, на вход которых подается сигнал с внутреннего генератора цифровой последовательности. Задавая значения параметров Generator Polynomial = [1 0 0 1 0 1], Initial States = [1 1 0 1 0] и Sample Time = 1e-3, получаем информационное сообщение с длительностью символа 1мс в виде машинного кода NRZ-L:

![]() .

.

2.1

Исходная цифровая последовательность перекодируется в марковский код NRZ-M. Использованная подсистема представлена на рисунке 2.

Рисунок 2 — Структура подсистемы Subsystem1 Coder

Принцип перекодирования в NRZ-M код заключается в следующем: при получении единицы символ цифрового сообщения изменяется на противоположный, а при получении нуля – не изменяется. В цифровой технике этот принцип реализован в Т-триггере, который получается из JK-триггера путем подачи сообщения на оба входа. На вход CLK подается меандр с периодом 1 мс.

Диаграммы входного сигнала и перекодированного с выхода триггера приведены на рисунке 3.

Рисунок 3 — Временные диаграммы перекодирующей подсистемы

Следующим этапом является преобразование цифровой последовательности в биполярный вид. Математическая модель системы, выполняющей данную операцию, представлена блоком Unipolar to Bipolar Converter. Сигнал, поступающий на вход такого блока, растягивается по амплитуде в два раза и центрируется относительно нуля.

2.1

2.2

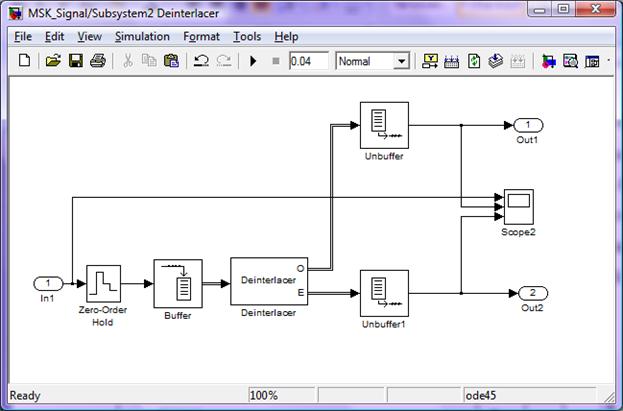

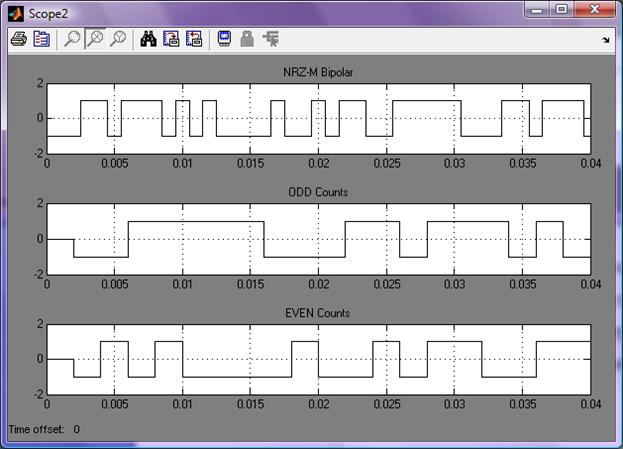

Разделение на синфазный и квадратурный каналы осуществляется в подсистеме Subsystem2 Deinterlacer.

Рисунок 4 — Структура подсистемы Subsystem2 Deinterlacer

Основным блоком в данной подсистеме является блок Deinterlacer, осуществляющий разделение входного сигнала и генерирование двух выходных сигналов. В данном примере входная последовательность представлена одномерным вектором, поэтому применяется блок Buffer, преобразующий входную последовательность в двухэлементный вектор, который и обрабатывается в блоке Deinterlacer. Блоки Unbuffer преобразуют обе последовательности в одноэлементные векторы для дальнейшей обработки.

Особенностью блока Deinterlacer является то, что одновременно с разделением цифрового сообщения на четные и нечетные биты удваивается длительность одного символа, что позволяет сохранить исходную скорость передачи.

Также стоит отметить, что задержка, вызванная работой триггера выравнивается до длительности одиночного символа.

Рисунок 5 — Временные диаграммы работы подсистемы Subsystem2 Deinterlacer

После разделения цифровые последовательности «сглаживаются» гармоническими колебаниями: синусоидой в синфазном канале и косинусоидой – в квадратурном. «Сглаживание» достигается простым перемножением входной последовательности и гармонического колебания в блоках Product. Частота колебаний выбирается таким образом, чтобы длительность полупериода соответствовала длительности одного информационного символа, т.е. 500 Гц. Цифровая последовательность в квадратурном канале задерживается на половину длительности цифрового символа для предотвращения разрывов амплитуды импульсов при сглаживании.

Структура подсистемы, выполняющей «сглаживание» и временные диаграммы ее работы приведены на рисунке 6.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.