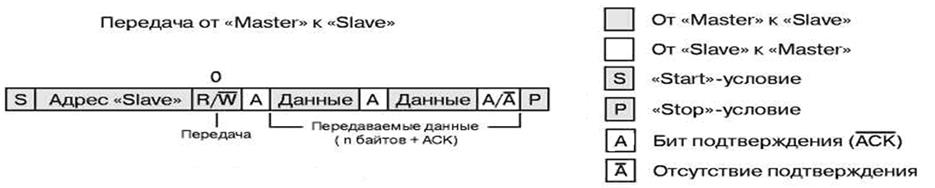

Каждое устройство, участвующее в обмене данными по шине I2C, должно иметь свой уникальный адрес (байт), по которому оно распознает адресованные ему пакеты данных. Поскольку адресных линий в шине I2C нет, а все имеющиеся устройства подключены к двум общим для всех них линиям SCL (синхронизация) и SDA (данные), как показано и на рис. 3.1, то байт адреса передается ведущим устройством («Master») в начале каждого цикла передачи данных (рис.3.2). Распознав свой адрес, соответствующее ведомое устройство («Slave») отвечает ведущему битом подтверждения «А», после чего ведущее устройство начинает передавать ведомому (или принимать от ведомого) байты информации. Пересылка каждого байта должна заканчиваться таким же битом подтверждения «А».

Рис. 3.2

Начинается цикл обмена Start-условием, заканчивается Stop-условием. Оба эти условия, как и бит подтверждения, на шине I2C задаются определенным сочетанием фронтов и уровней на линиях SDA и SCL. Программа, формирующая пакеты информации по этим правилам, находится в микроконтроллере лабораторного макета.

Как правило, устройства, управляемые по шине I2C, выпускаются с уже записанными в них Slave-адресами. У ИМС TSA6057 предусмотрена возможность выбора одного из двух адресов, в зависимости от значения логического уровня на выводе AS микросхемы (рис. 3.1):

- AS = 0 Slave-address = 110001002 = C416;

- AS = 1 Slave-address = 110001102 = C616.

В лабораторном макете, как видно из схемы рис. 3.1, вывод AS подключен к высокому уровню, поэтому начинать обращение к ИМС синтезатора следует только со Slave-адреса 11000110, в противном случае синтезатор не станет реагировать на передаваемые ему команды.

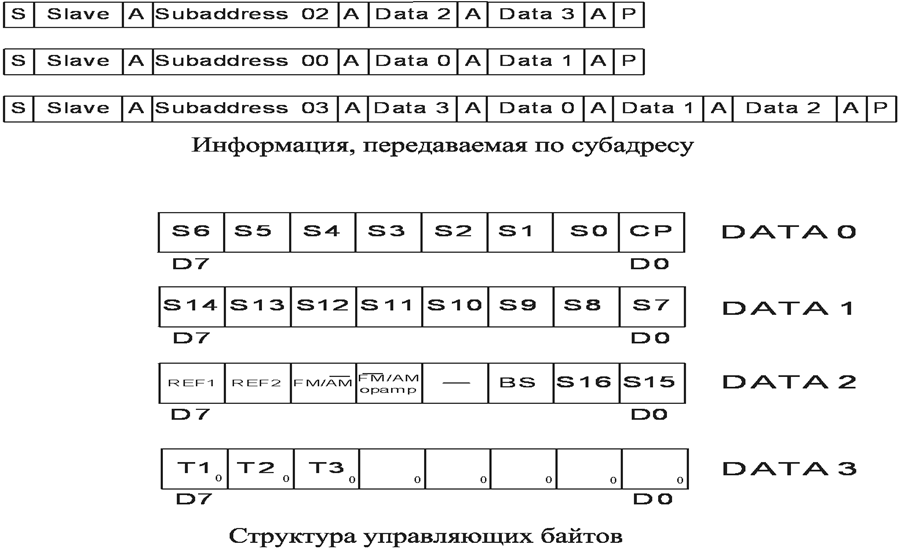

Управляющие байты ИМС TSA6057 бывают четырех типов, называются они DATA0, DATA1, DATA2, DATA3, в каждом из них содержится свойственная только этому байту информация (рис. 3.3).

Рис. 3.3

Возможны три комбинации управляющих байтов, они показаны в верхней части рис. 3.3. Под субадресом здесь понимается байт, который передается после Slave-адреса и принимает три возможных значения:

- 00000010, т.е. субадрес 02, если передаются DATA2, DATA3;

- 00000000, т.е. субадрес 00, если передаются DATA0, DATA1;

- 00000011, т.е. субадрес 03, если передаются DATA3, DATA0, DATA1, DATA2.

Последний формат самый полный, но для сокращения времени передачи информации иногда полезны и сокращенные форматы 02 или 00.

Что касается байта DATA3, то все его биты рекомендуется программировать нулями. Этот байт используется для тестирования при производстве микросхемы, пользователям он не нужен.

Напряжение, управляющее частотой ГУН, может подаваться с выхода ИМС TSA6057 либо с потенциометра, что необходимо для ручного управления частотой ГУН. Для переключения с ручного режима управления частотой на автоматический служит соответствующий тумблер на корпусе макета.

Внутренняя структура ИМС управления синтезатором TSA6057 показана на рис. 3.4. Из рисунка, в частности, ясно, что к этой микросхеме могут быть подключены два отдельных ГУН:

а) диапазона 0,512…30 МГц (этот диапазон называется в документации «АМ») – к выводам 15, 14, 7 (как на рис. 3.1);

б) диапазона 30…150 МГц (этот диапазон называется в документации «FМ») – к выводам 13, 14, 5.

В данной работе используется только один ГУН диапазона

«АМ», поэтому соответствующим выбором управляющих битов нужно обеспечить именно

его включение в петлю ФАПЧ синтезатора. Для этого ключ FM/AM

(подходящий к выводу 15) должен быть замкнут, а ключ AM/FM

(подключенный к выводу 13) – разомкнут. Состоянием этих ключей управляет бит,

называемый ![]() . Для выбора диапазона «АМ» он должен находиться в

состоянии «1». Это бит 4 управляющего

байта DАТА2.

. Для выбора диапазона «АМ» он должен находиться в

состоянии «1». Это бит 4 управляющего

байта DАТА2.

Кроме бита ![]() , необходимо правильно задать значение еще одного бита,

отвечающего за выбор диапазона синтезатора – это бит

, необходимо правильно задать значение еще одного бита,

отвечающего за выбор диапазона синтезатора – это бит ![]() ,

работающий следующим образом:

,

работающий следующим образом:

- при ![]() = 0 в качестве входного сигнала принимается

напряжение со входа 7 (вход буферного усилителя БУ1), как это сделано на рис.

3.1;

= 0 в качестве входного сигнала принимается

напряжение со входа 7 (вход буферного усилителя БУ1), как это сделано на рис.

3.1;

- при ![]() = 1 в качестве входного сигнала принимается

напряжение со входа 5 (вход буферного усилителя БУ2).

= 1 в качестве входного сигнала принимается

напряжение со входа 5 (вход буферного усилителя БУ2).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.