|

Введение 3

1. Сумматоры 3

2. Преобразователи кодов 6

2.1 Дешифраторы 8

2.2 Шифраторы 11

3. Мультиплексоры 11

4. Демультиплексоры 12 Список использованной литературы 14

ВВЕДЕНИЕ

Комбинационные микросхемы реализуют различные преобразования двоичных цифровых сигналов на основе комбинационных логических функций.

К основным типам таких устройств относятся сумматоры, дешифраторы, шифраторы, преобразователи кодов, схемы равнозначности кодов, схемы сравнения двоичных чисел, пороговые схемы и мажоритарные элементы, мультиплексоры и демультиплексоры и др.

Рассмотрим особенности функционирования и принципы построения этих устройств на базе дискретных элементов и интегральных микросхем.

1.КОМБИНАЦИОННЫЕ СУММАТОРЫ

Сумматором называется устройство, образующее сумму двух чисел на

выходе, представленных сигналами на его входах.

Существующие сумматоры можно классифицировать по ряду различных признаков:

1. По способу реализации суммирующей схемы. Здесь можно выделить две разновидности сумматоров – комбинационные и накопительные. В комбинационном сумматоре результат суммирования присутствует только в течение времени действия входных сигналов. Комбинационные сумматоры состоят из набора логических схем, реализующих функции суммы и переноса.

Накопительные сумматоры имеют элементы памяти, обеспечивающие

длительное хранение результатов суммирования.

2. По способу обработки многоразрядных чисел;

3. По способу реализации переноса и т.д.

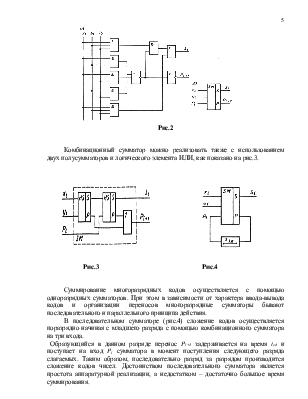

Операция суммирования осуществляется в сумматорах поразрядно с использованием одноразрядных суммирующих схем. При этом в каждом требуется выполнить сложение трех двоичных цифр: цифры данного разряда первого слагаемого xi , цифры этого же разряда второго слагаемого yi и цифры переноса Pi из соседнего младшего разряда.

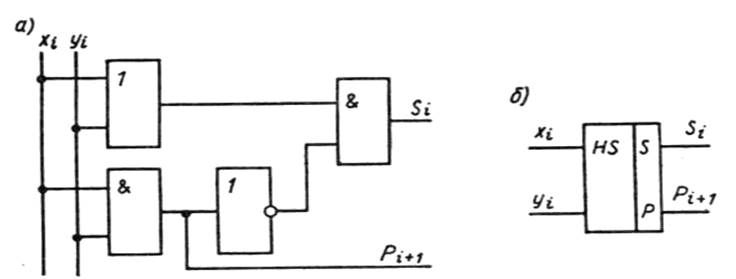

Иногда такое суммирование разбивают на две аналогичные операции: суммирование двух цифр слагаемых и суммирование полученного результата с переносом из соседнего младшего разряда. Каждая из этих операций выполняется схемой, называемой полусумматором. Т.е. полусумматор – это устройство с двумя входами и двумя выходами, соотношение между входными и выходными сигналами которых определяется функцией неравнозначности. А объединение двух полусумматоров позволяет получить полный сумматор.

На рис.1, а, б приведены функциональная схема полусумматора и условное его обозначение . Схема является комбинационной и реализуется на логических элементах.

Логика работы одноразрядного сумматора на три входа или полного сумматора приведена в табл.2, где xi и yi – суммируемые двоичные цифры в i – м разряде, Pi – перенос из младшего разряда, Si – образующаяся сумма в данном разряде, Pi+1 – перенос в соседний старший разряд. Табл. 1

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.