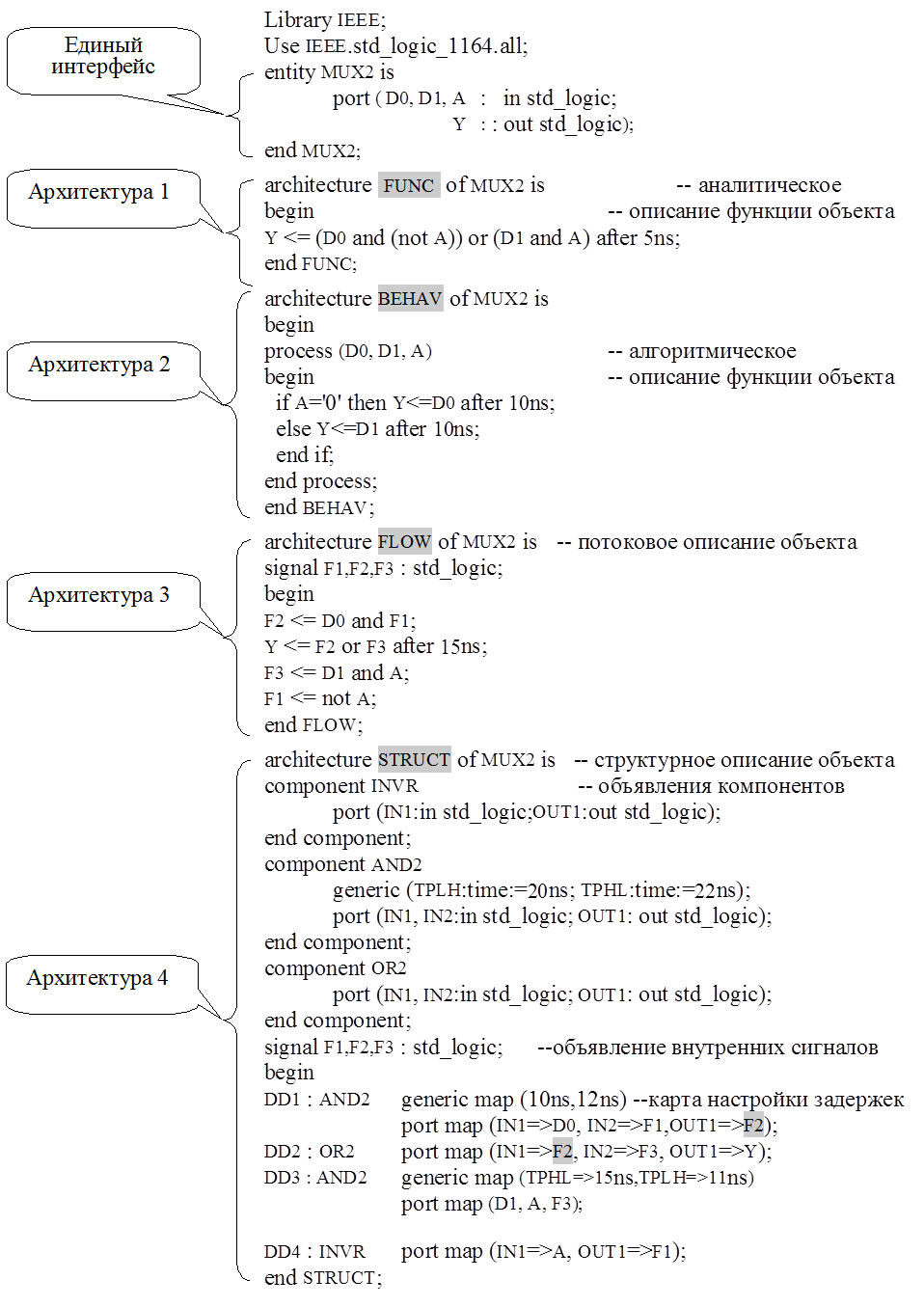

Первое, что приходит в голову, это построить VHDL-модель мультиплексора (рис.8, а) по образу и подобию ранее созданной модели элемента AND2 (рис.1). И там и здесь используется логическая функция объекта, а потому мы назовём архитектурное тело именем FUNC (от слова functional).

При построении этой модели объект проекта рассматривался как примитив (чёрный ящик), его структурная организация не представляла для нас никакого интереса. Всё что нам требовалось - это зависимость выхода от входов, представленная логическим уравнением. Такое описание работы моделируемого объекта называется аналитическим.

К сожалению, для сложных объектов аналитическое описание получить очень трудно или невозможно вовсе. Поэтому вынужденно его приходится заменять алгоритмическим. Конечно, алгоритм всегда можно реализовать в виде функции или процедуры, но в языке VHDL есть для этих целей более эффективный инструмент. Он называется механизмом процессов. Оказывается кроме описания алгоритмов на абстрактном уровне – это ещё и великолепный способ моделировать параллельные операции.

Детально мы поговорим о нём позднее, а сейчас прокомментируем только самое необходимое. На рис.8 процесс используется в архитектуре 2. Она называется BEHAV (от слова behavior - поведение).

Описание процесса начинается с ключевого слова process, за которым в круглых скобках следует так называемый список сигналов запуска. Процесс запускается только в том случае, когда хотя бы один из сигналов названного списка меняет своё значение. Операторы активного процесса выполняются последовательно один за другим, как в обычных процедурах. В нашем примере процесс включает единственный условный оператор.

Возникает, правда, законный вопрос, а могли ли мы подобным образом, то есть с помощью процессов, описать работу ранее рассмотренного логического элемента AND2? Думаю, что вы сами знаете ответ. Вот только модель получится более громоздкой.

Подведём некоторые итоги. Для структурных примитивов, рассматриваемых как чёрный ящик, возможно только поведенческое (функциональное или алгоритмическое) описание объекта. Рассмотренными примерами (архитектуры 1 и 2) мы исчерпали эти возможности.

Для более сложных объектов с известной структурой (или несколькими структурными решениями) появляются дополнительные ресурсы.

Во-первых, используя структурные данные, можно построить потоковую модель. Она реализована в архитектуре 3, имеющей имя FLOW (поток).

Во-вторых, на основании структурной информации можно построить чисто структурную модель. Она представлена архитектурой 4 и называется STRUCT (от слова structural - структурный). Фактически такая модель представляет собой список составных частей объекта (компонентов) и связей между ними, записанных в формате VHDL. Современные САПР умеют автоматически генерировать такой список, конвертируя электрическую схему цифровой аппаратуры в VHDL-код.

Структурная модель (архитектура 4) выглядит довольно тяжеловесно, и этому есть объяснение. Значительную часть архитектурного тела составляет раздел деклараций, где перечисляются все типы компонентов, используемых в моделируемом объекте. В нашем примере их три – это INVR, AND2 и OR2. Кроме того, здесь же объявляются и все внутренние сигналы схемы F1, F2 и F3.

Описание компонента (некоего шаблона) фактически повторяет интерфейс соответствующего объекта проекта и имеет то же самое имя. Да иначе и быть не может – ведь речь идёт об одном физическом объекте. Чтобы убедиться в сказанном, достаточно взглянуть на модель AND2 (рис.4) и сравнить её описание с компонентом AND2 на рис.8.

Компоненты INVR и OR2 тоже ссылаются на соответствующие VHDL-модели, которых к моменту написания этого текста ещё не существует. Надеюсь, что вы их построите самостоятельно, используя в качестве «прототипа» модель элемента AND2, показанную на рис.1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.