Министерство образования и науки РФ

Новосибирский Государственный Технический Университет

Кафедра ВТ

Курсовой проект по дисциплине

«Моделирование»

Факультет: АВТ

Группа: АМ-411

Студент: Гребенникова М.Ю.

Преподаватель: Шалагинов А. В.

Новосибирск, 2007 г

Создать структурные и поведенческие модели цифрового узла в пакетах DesignLab 8, OrCAD 9.1, Active HDL 6.2. Провести имитационные эксперименты с разработанным узлом. Целью экспериментов является подтверждение работоспособности узла и соответствие его временных задержек требуемым.

Произвести сравнительный анализ использованных инструментальных средств проектирования.

Исследуемый цифровой узел: ИД7 — высокоскоростной дешифратор – демультиплексор, преобразующий трехразрядный код А0-А2 в напряжение низкого логического уровня, появляющееся на одном из восьми выходов. DC имеет трехвходовой логический элемент разрешения. Зарубежный аналог — DM74LS138.

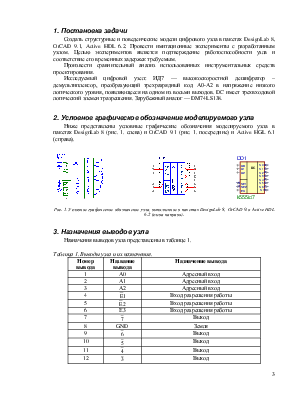

Ниже представлены условные графические обозначения моделируемого узла в пакетах DesignLab 8 (рис. 1. слева) и OrCAD 9.1 (рис. 1. посередине) и Active HGL 6.1 (справа).

|

|

|

|

Рис. 1. Условное графическое обозначение узла, выполненное в пакетах DesignLab 8, OrCAD 9. и Active HDL 6.2 (слева направо).

Назначения выводов узла представлены в таблице 1.

Таблица 1. Выводы узла и их назначения.

|

Номер вывода |

Название вывода |

Назначение вывода |

|

1 |

А0 |

Адресный вход |

|

2 |

А1 |

Адресный вход |

|

3 |

А2 |

Адресный вход |

|

4 |

|

Вход разрешения работы |

|

5 |

|

Вход разрешения работы |

|

6 |

Е3 |

Вход разрешения работы |

|

7 |

|

Выход |

|

8 |

GND |

Земля |

|

9 |

|

Выход |

|

10 |

|

Выход |

|

11 |

|

Выход |

|

12 |

|

Выход |

|

13 |

|

Выход |

|

14 |

|

Выход |

|

15 |

|

Выход |

|

16 |

VCC |

Напряжение питания |

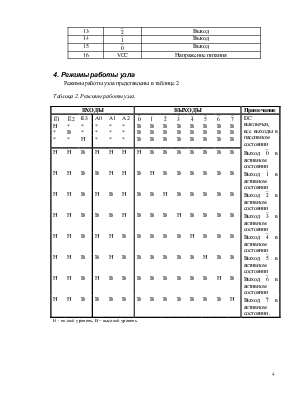

Режимы работы узла представлены в таблице 2.

Таблица 2. Режимы работы узла.

|

ВХОДЫ |

ВЫХОДЫ |

Примечание |

||||||||||||

|

|

|

E3 |

A0 |

A1 |

A2 |

|

|

|

|

|

|

|

|

DC выключен, все выходы в пассивном состоянии |

|

Н |

* |

* |

* |

* |

* |

В |

В |

В |

В |

В |

В |

В |

В |

|

|

* |

В |

* |

* |

* |

* |

В |

В |

В |

В |

В |

В |

В |

В |

|

|

* |

* |

Н |

* |

* |

* |

В |

В |

В |

В |

В |

В |

В |

В |

|

|

Н |

Н |

В |

Н |

Н |

Н |

Н |

В |

В |

В |

В |

В |

В |

В |

Выход |

|

Н |

Н |

В |

В |

Н |

Н |

В |

Н |

В |

В |

В |

В |

В |

В |

Выход |

|

Н |

Н |

В |

Н |

В |

Н |

В |

В |

Н |

В |

В |

В |

В |

В |

Выход |

|

Н |

Н |

В |

В |

В |

Н |

В |

В |

В |

Н |

В |

В |

В |

В |

Выход |

|

Н |

Н |

В |

Н |

Н |

В |

В |

В |

В |

В |

Н |

В |

В |

В |

Выход |

|

Н |

Н |

В |

В |

Н |

В |

В |

В |

В |

В |

В |

Н |

В |

В |

Выход |

|

Н |

Н |

В |

Н |

В |

В |

В |

В |

В |

В |

В |

В |

Н |

В |

Выход |

|

Н |

Н |

В |

В |

В |

В |

В |

В |

В |

В |

В |

В |

В |

Н |

Выход |

Н - низкий уровень, В – высокий уровень.

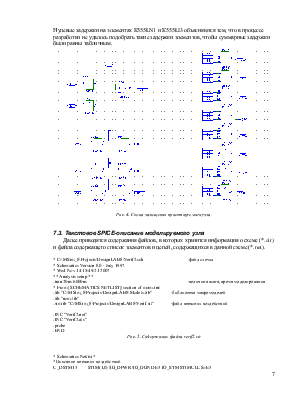

Максимальные задержки распространения сигналов микросхемы K555ИД7 (задержки взяты у зарубежного аналога DM74LS138, произведенного Firechild Semiconductor) представлены в таблице 3.

Таблица 3. Максимальные задержки распространения микросхемы К555ИД7.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.