Рис. 5. Содержимое файла verif2.cir

* Schematics Netlist *

*Описание внешних воздействий

U_DSTM13 STIM(1,0) $G_DPWR $G_DGND E3 IO_STM STIMULUS=E3

U_DSTM14 STIM(1,0) $G_DPWR $G_DGND NE2 IO_STM STIMULUS=NE2

U_DSTM15 STIM(1,0) $G_DPWR $G_DGND NE1 IO_STM STIMULUS=NE1

U_DSTM16 STIM(1,0) $G_DPWR $G_DGND A2 IO_STM STIMULUS=A2

U_DSTM17 STIM(1,0) $G_DPWR $G_DGND A1 IO_STM STIMULUS=A1

U_DSTM18 STIM(1,0) $G_DPWR $G_DGND A0 IO_STM STIMULUS=A0

*Описание элементов схемы с указанием позиционных обозначений

X_DD4_DD1_1 DD4_S4 DD4_S5 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD1_2 DD4_S2 DD4_S3 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD1_3 A0 DD4_S4 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD1_4 A1 DD4_S2 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD2_1 DD4_S5 DD4_S6 DD4_S2 DD4_S0 N1 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD2_2 DD4_S6 DD4_S4 DD4_S3 DD4_S0 N2 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD3_1 DD4_S6 DD4_S5 DD4_S3 DD4_S0 N3 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD3_2 DD4_S6 DD4_S4 DD4_S2 DD4_S1 N4 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD4_1 DD4_S6 DD4_S5 DD4_S2 DD4_S1 N5 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD1_5 DD4_S0 DD4_S1 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD1_6 A2 DD4_S0 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD5_1 NE2 $N_0001 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD5_2 NE1 $N_0002 $G_DPWR $G_DGND K555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD6_1 E3 $N_0001 $N_0002 DD4_S6 $G_DPWR $G_DGND K555LI3 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD4_2 DD4_S6 DD4_S4 DD4_S3 DD4_S1 N6 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD7_1 DD4_S6 DD4_S4 DD4_S2 DD4_S0 N0 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD4_DD7_2 DD4_S6 DD4_S5 DD4_S3 DD4_S1 N7 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Рис.6. Содержимое файла verif2.net

7.4. Содержимое файла описания внешних воздействий

* C:\MSim_8\Projects\DesignLAB8\Verif.stl written on Wed Nov 14 15:31:17 2007

* by Stimulus Editor -- Serial Number: 100617 -- Version 8.0

;!Stimulus Get

;! A0 Digital A1 Digital A2 Digital NE1 Digital NE2 Digital E3 Digital - Инициализация

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 6us

;!AutoUniverse

;!XminRes 400ns

;!YminRes 1n

;!Ok

.STIMULUS A0 STIM (1, 1) -Определение сигнала А0

+ +0s 0

+ 1.2us 1

+ 1.6us 0

+ 2us 1

+ 2.4us 0

+ 2.8us 1

+ 3.2us 0

+ 3.6us 1

+ 4us 0

.STIMULUS A1 STIM (1, 1) -Определение сигнала А1

+ +0s 0

+ 1.6us 1

+ 2.4us 0

+ 3.2us 1

+ 4us 0

.STIMULUS A2 STIM (1, 1) -Определение сигнала А2

+ +0s 0

+ 2.4us 1

+ 4us 0

.STIMULUS NE1 STIM (1, 1) -Определение сигнала NE1

+ +0s 0

+ 4.8us 1

.STIMULUS NE2 STIM (1, 1) -Определение сигнала NE2

+ +0s 0

+ 5.6us 1

.STIMULUS E3 STIM (1, 1) -Определение сигнала E3

+ +0s 1

+ 400ns 0

+ 800ns 1

+ 1.2us 1

Рис 7. Содержимое файла verif.stl

Рис.8.Временная диаграмма входных сигналов.

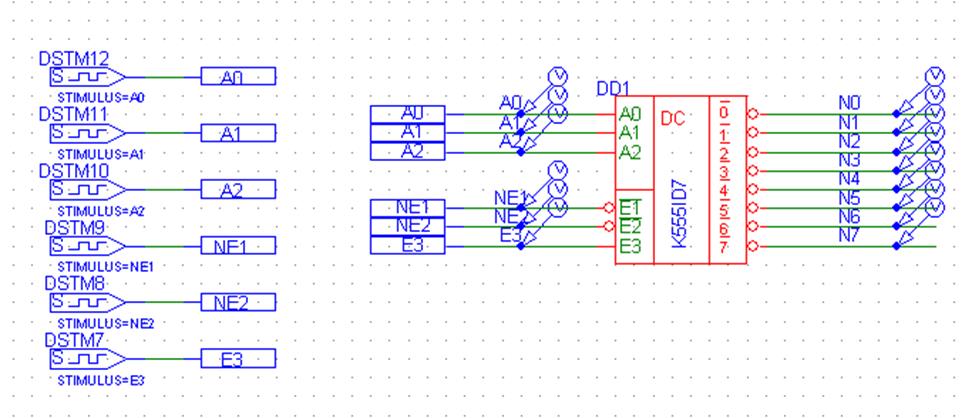

7.5. Схема верификации иерархического символа

Схема верификации иерархического символа представлена на рис.9.

Рис. 9. Схема верификации иерархического символа.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.