(Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7)<=Q_INT;

END model;

Рис 25. Поведенческая VHDL-модель узла

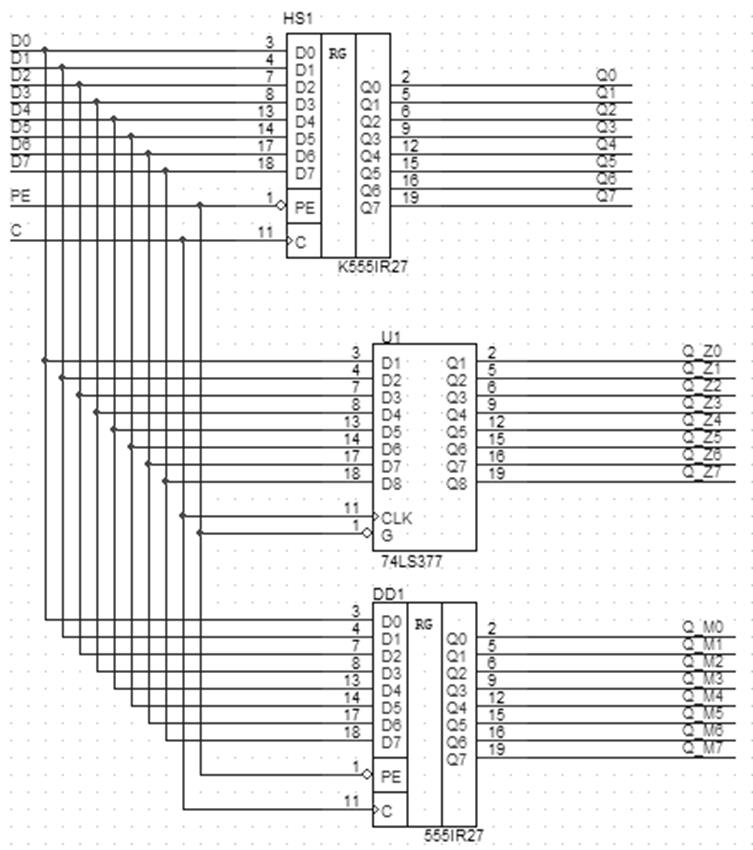

Рис 26. Схема верификации узла с подключенной VHDL-моделью (DD1), зарубежным аналогом (74LS377) и элемента со схемой замещения (HS1).

Протестируем для наглядности и сравнении задержек VHDL-моделью (DD1), зарубежный аналог (74LS377) и элемент со схемой замещения (HS1).

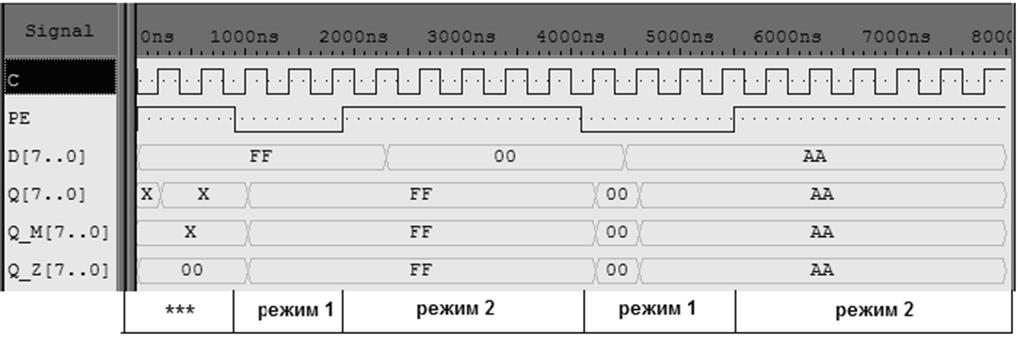

Рис 27. Временные диаграммы

моделирования VHDL-модели узла (DD1), зарубежного

аналога (74LS377) и элемента со схемой замещения (HS1).

Рис 27. Временные диаграммы

моделирования VHDL-модели узла (DD1), зарубежного

аналога (74LS377) и элемента со схемой замещения (HS1).

Режим 1 – запись (вход PE устанавливается в L состояние)

Режим 2 – хранение (вход PE устанавливается в H состояние)

C – Синхронный тактовый вход.

PE – Вход разрешения.

D(7..0) – Вход информационный.

Q(7..0) – Выход информационный (схема замещения).

Q_M(7..0) – Выход информационный (VHDL-модель).

Q_Z(7..0) – Выход информационный (зарубежный аналог 74LS377).

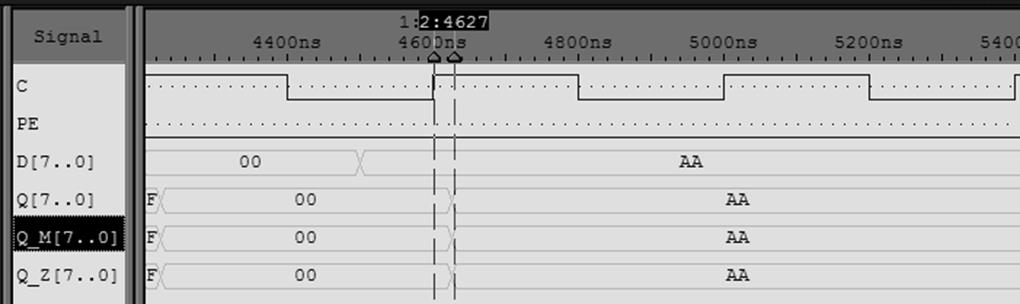

Время задержки распространения сигнала при выключении и включении от входа С к выходу Q7…Q0 равны по 27нс.

Рис 28. Временная диаграмма задержки VHDL-модели узла (DD1) при моделировании. (27нс)

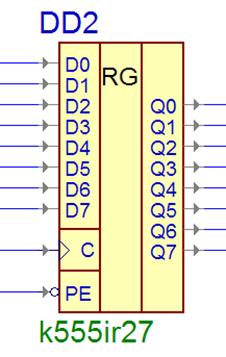

Иерархический символ проектируемого узла представлен на рис. 27.

Рис 29. Условное графическое изображение узла в виде иерархического символа

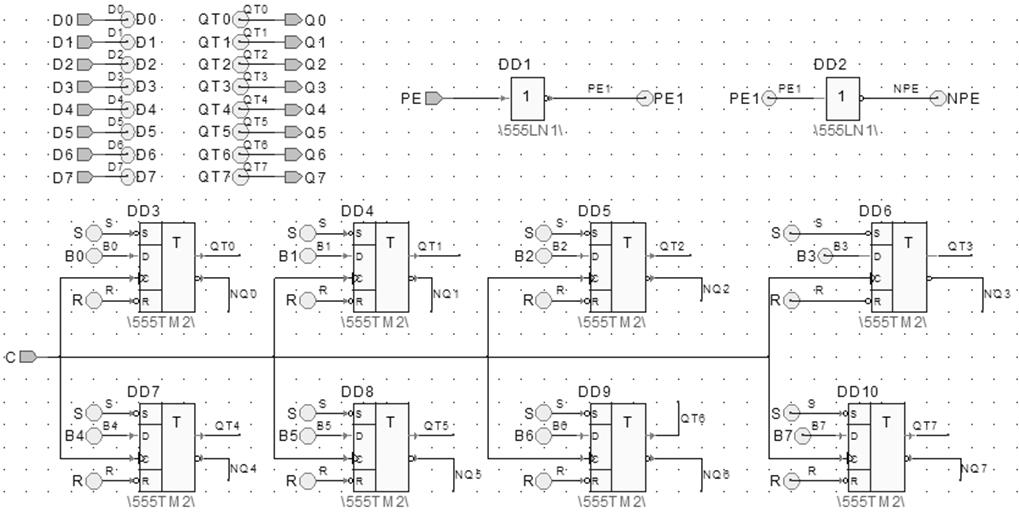

Рис 30. Принципиальная схема замещения узла часть №1

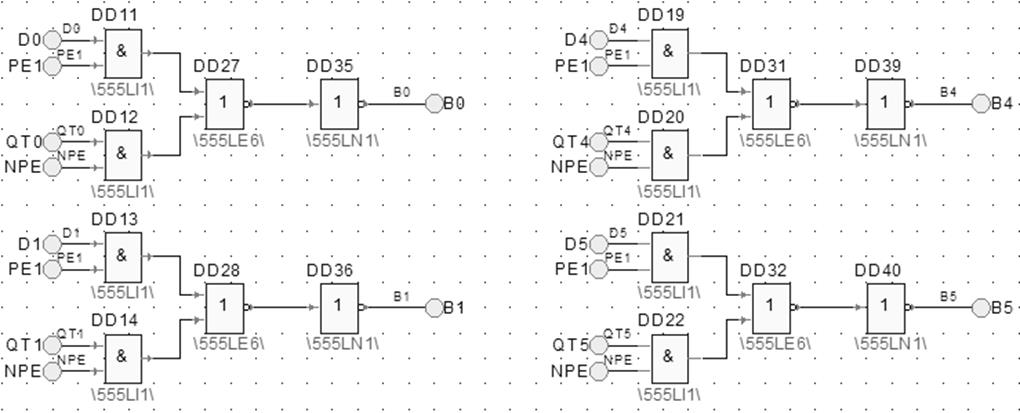

Рис 31. Принципиальная схема замещения узла часть №2

|

library IEEE; use IEEE.STD_LOGIC_1164.all; entity K555IR27_VHD is port( PE : in STD_LOGIC; C : in STD_LOGIC; D7 : in STD_LOGIC; D6 : in STD_LOGIC; D5 : in STD_LOGIC; D4 : in STD_LOGIC; D3 : in STD_LOGIC; D2 : in STD_LOGIC; D1 : in STD_LOGIC; D0 : in STD_LOGIC; Q7 : out STD_LOGIC; Q6 : out STD_LOGIC; Q5 : out STD_LOGIC; Q4 : out STD_LOGIC; Q3 : out STD_LOGIC; Q2 : out STD_LOGIC; Q1 : out STD_LOGIC; Q0 : out STD_LOGIC ); end K555IR27_VHD; --}} End of automatically maintained section architecture K555IR27_VHD of K555IR27_VHD is signal Q_INT : std_logic_vector (0 to 7); begin process(D0,D1,D2,D3,D4,D5,D6,D7,C,PE) begin IF PE = '1' and C = '1' and C'EVENT then Q_INT(0 to 7) <= Q_INT(0 to 7) after 17ns; elsif PE = '0' and C = '1' and C'EVENT then Q_INT(0)<=D0 after 27ns; Q_INT(1)<=D1 after 27ns; Q_INT(2)<=D2 after 27ns; Q_INT(3)<=D3 after 27ns; Q_INT(4)<=D4 after 27ns; Q_INT(5)<=D5 after 27ns; Q_INT(6)<=D6 after 27ns; Q_INT(7)<=D7 after 27ns; end if; end process; (Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7)<=Q_INT; end K555IR27_VHD; |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.