Входы А,В – выход S - 24нс.

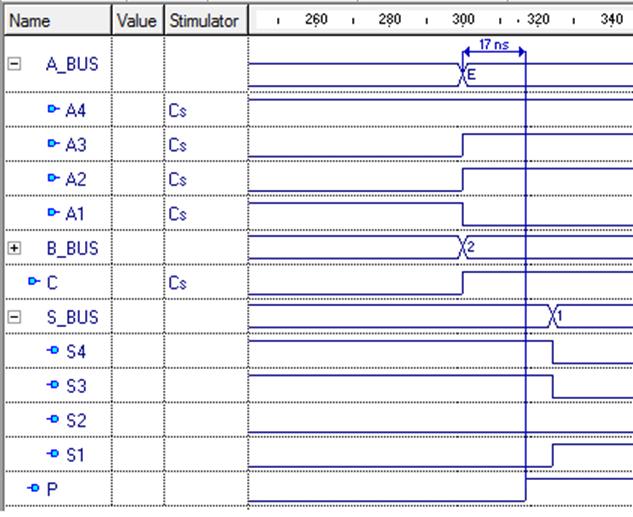

Рис. 43. Время задержки распространения сигнала при включении:

Вход C – выход P - 17нс.

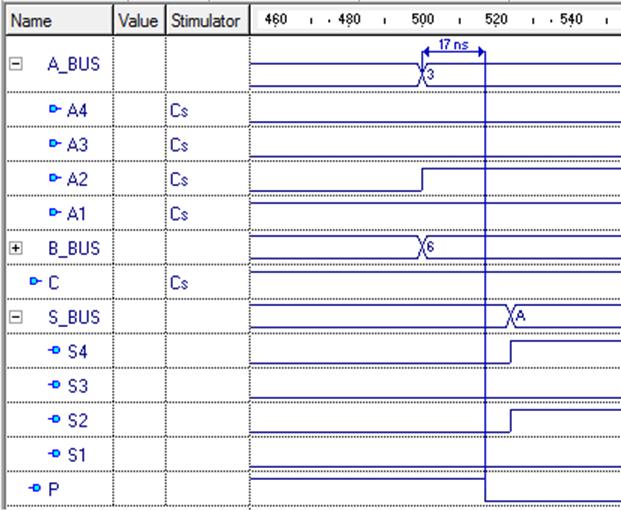

Рис. 44. Время задержки распространения сигнала при выключении:

Вход C – выход P - 17нс.

Исходя из результатов эксперимента, можно прийти к выводу, что VHDL-модель работает корректно. Все задержки, показанные на временных диаграммах совпадают с табличными, что является подтверждением правильности их имитации.

В ходе данной курсовой работы было выполнено индивидуальное задание по разработке цифрового узла ИМ3, созданию его поведенческой модели на языке VHDL в пакетах OrCAD 9.1 и Active-HDL 8.1. Мной были проведены имитационные эксперименты с разработанным узлом, чтобы подтвердить правильность его работы, а также проверить соответствие его временных задержек требуемым. В процессе работы, были закреплены навыки и знания в области применения САПР OrCAD 9.1 и Active-HDL 8.1, проектирования цифровых устройств, программирования на языке описания цифровой аппаратуры VHDL, анализа результатов работы. Процесс выполнения работы охватил верификацию проекта, анализ и представление результатов, и достижение эталонной работы устройства. Работа была выполнена успешно, все требуемые задачи были выполнены.

В обоих пакетах САПР я уже работал неоднократно, и каждый раз сталкивался с одними и теми же проблемами. Как всегда OrCAD 9.1 во время работы несколько раз самопроизвольно закрывался из-за непонятной ошибки, и такое поведение одинаково что и на ОС Win XP, что на Win 7. Но, я, наученный «горьким» опытом, постоянно сохранялся, что помогло избежать в пустую потраченного времени. Не смотря на это, OrCAD 9.1, несомненно, мощнейший пакет, с большим количеством возможностей, включающий много разнообразных модулей и при этом, вся эта система работает довольно «шустро», не «съедая» все ресурсы ОС. Active-HDL, напротив, потребляет больше ресурсов, чем OrCAD, возможно это связано с тем, что Active-HDL реализован как единое пространство для проектирования, а не модульно как OrCAD.

В процессе работы с пакетами, выяснилось, что в OrCAD можно отменить только одно последнее действие, в отличии от Active-HDL, я считаю это неприемлемым для такого серьезного САПР. С точки зрения сборки схем оба пакета достаточно удобны и просты. Необязательно соединять проводники, чтобы показать их принадлежность к одной цепи, а достаточно присвоить им одинаковые имена. Что примечательно в Active-HDL, при создании схемы с помощью дизайнера BDE, создается пустой лист с указанными входами и выходами, и автоматически формируется иерархический символ, который является оболочкой этой схемы, это удобно, в OrCAD необходимо создавать оболочку вручную, или рисовать иерархический блок, что требует некие манипуляции, отнимающие время.

В OrCAD есть так называемый кэш проекта, который необходимо постоянно обновлять или очищать, при изменении символов в библиотеках, чтобы применить изменения, что также отнимает время и я про него постоянно забывал, в Active-HDL при сохранении изменений, они сразу применяются.

По поводу задания стимулов Active-HDL показался удобнее, так как здесь поддерживается одновременное задание сигналов, как графическим способом, так и прописыванием переключений. И измерять задержки в Active-HDL гораздо удобнее и нагляднее, чем в OrCAD, тем более, можно измерить столько задержек сколько нужно и при этом они все будут отображаться.

На счет VHDL-кода можно сказать, что не всегда написанный код в OrCAD сразу же заработает в Active-HDL, ввиду небольших особенностей, например, у меня написанный в OrCAD код не заработал в Active-HDL из-за применения имен моделей такого вида: «/K555LA3/», то есть имя модели нельзя начать с символа «/», также комментарии к коду вызвали «недовольствие» у Active-HDL. Но эти мелкие недочеты легко устраняются после компиляции, где по итогам компиляции можно понять в каком месте ошибка, а в OrCAD можно проверить только правильность синтаксиса, и если он не правилен, то надо будет уже выискивать ошибку самому. Что примечательно, что в Active-HDL есть утилита IPCORE Generator, с помощью которой можно автоматически сгенерировать VHDL или Verilog код, какого либо цифрового элемента.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.