В результате выполнения пункта задания и проведения эксперимента над VHDL-моделью были имитированы реальные задержки цифрового узла ИМ3, что подтверждают результаты верификации.

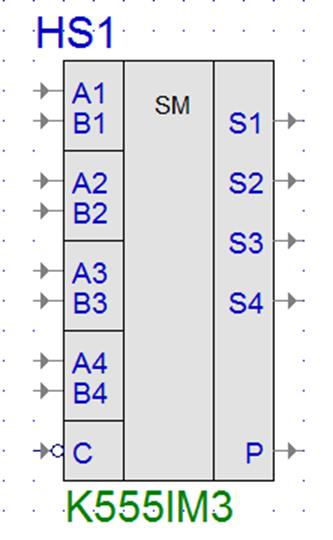

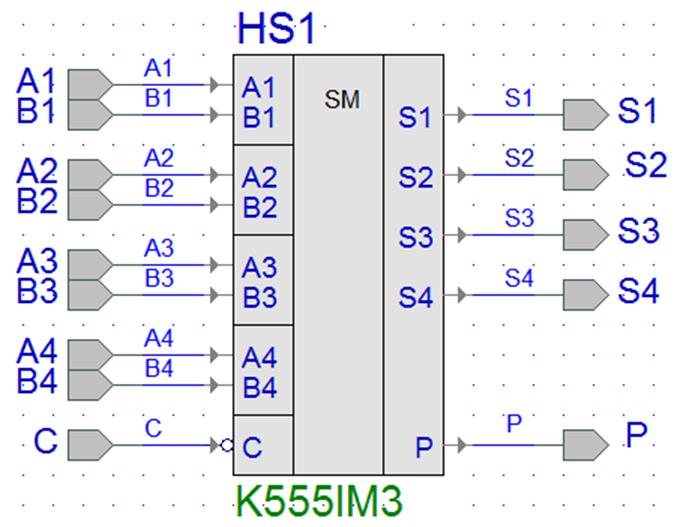

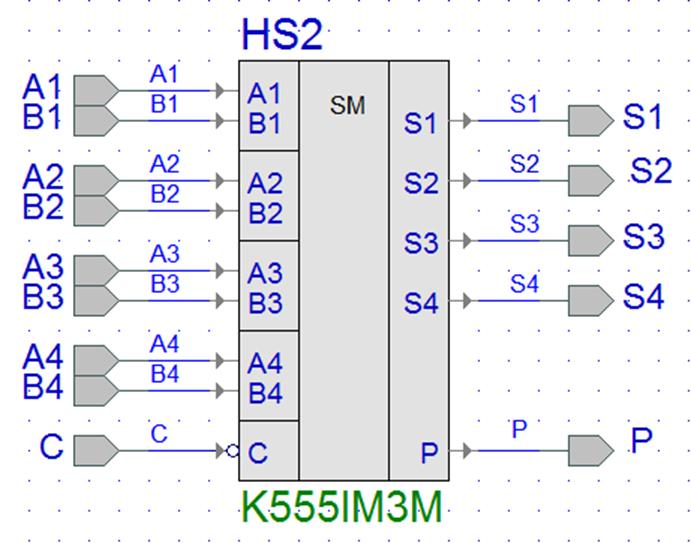

Ниже приведено УГО иерархического символа, поддерживаемого схемой замещения (рис. 28).

Рис. 28. Условное графическое изображение узла в виде иерархического символа.

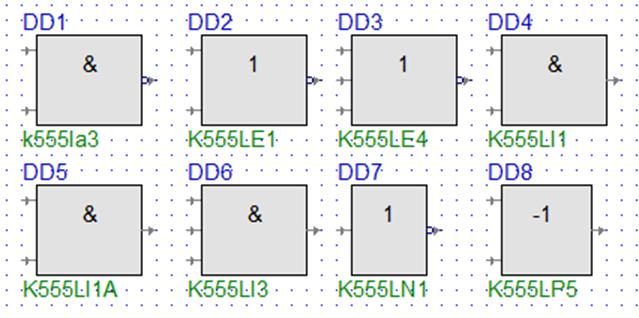

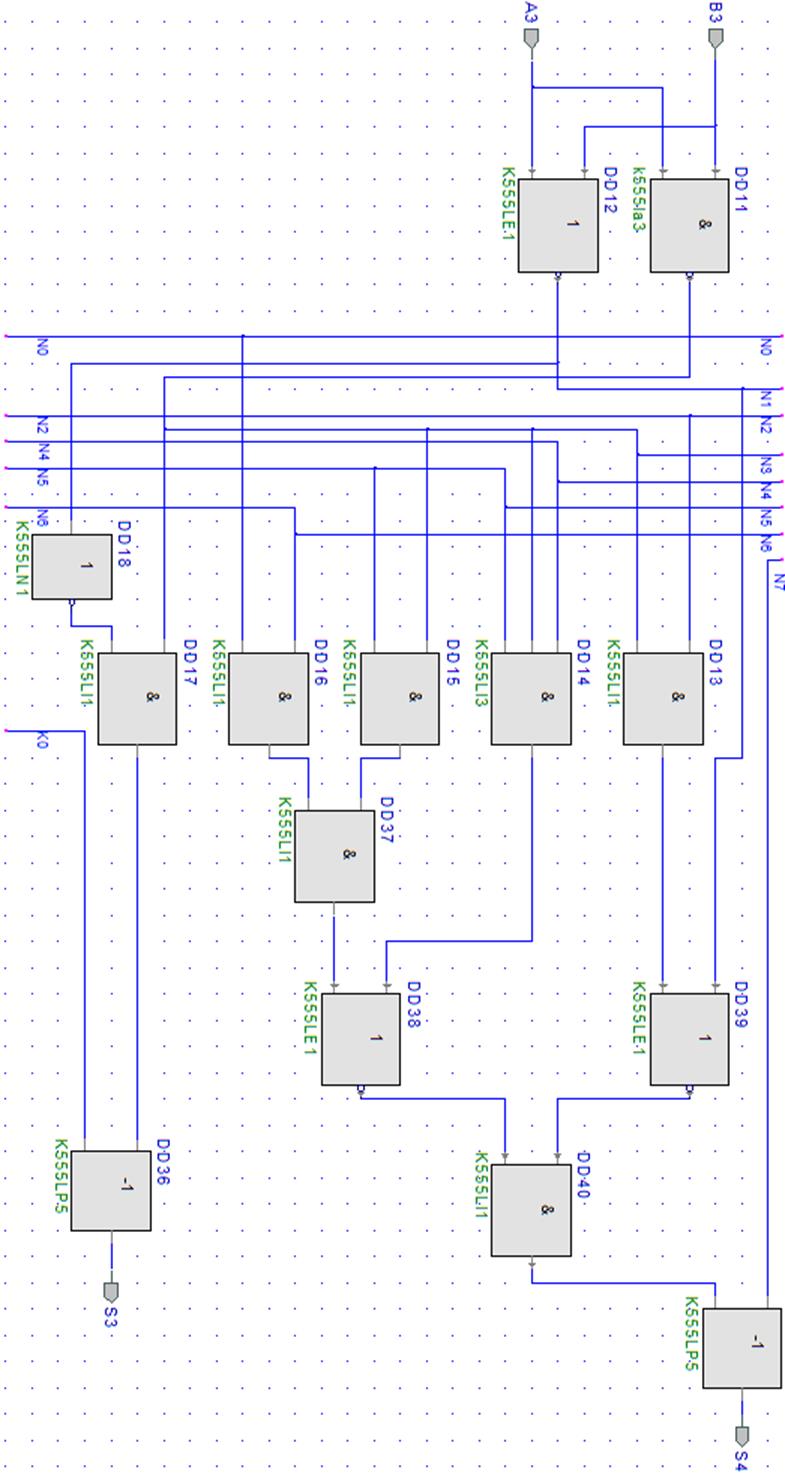

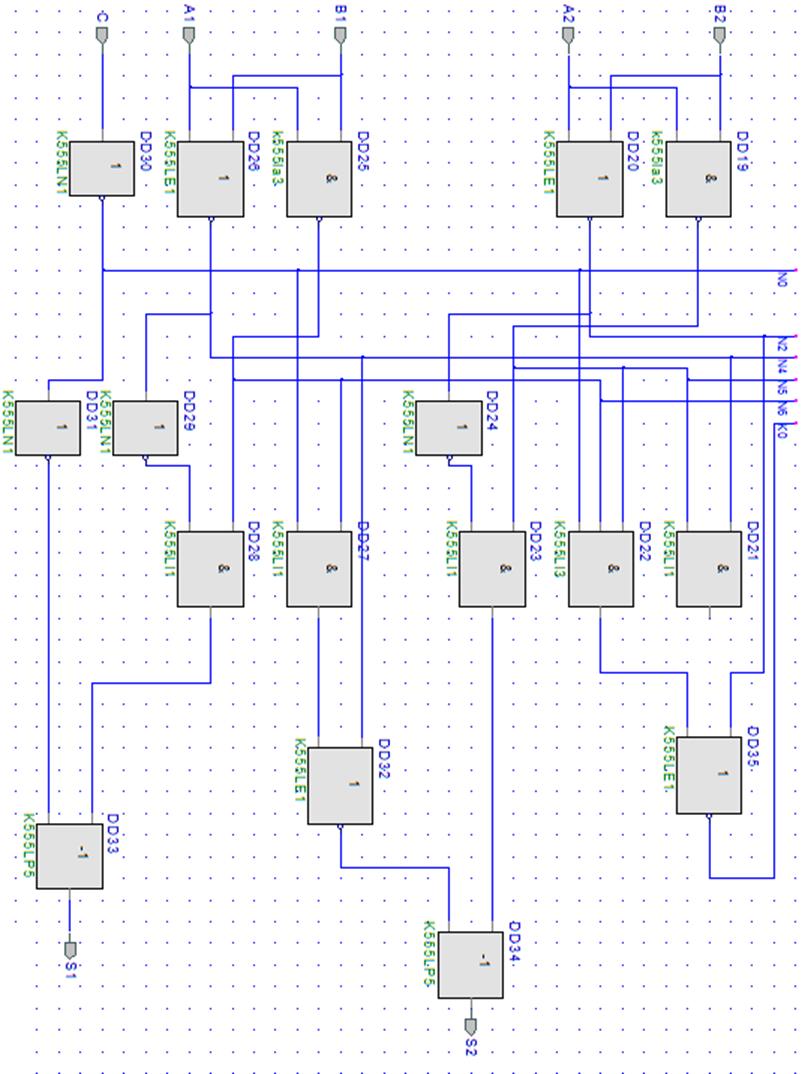

В схеме замещения используются элементы из таблицы 4, УГО элементов представлено на рисунке 29.

Рис.29. УГО символов, спроектированных для реализации схемы замещения ИМ3.

VHDL-модели данных элементов представлены в приложении 2.

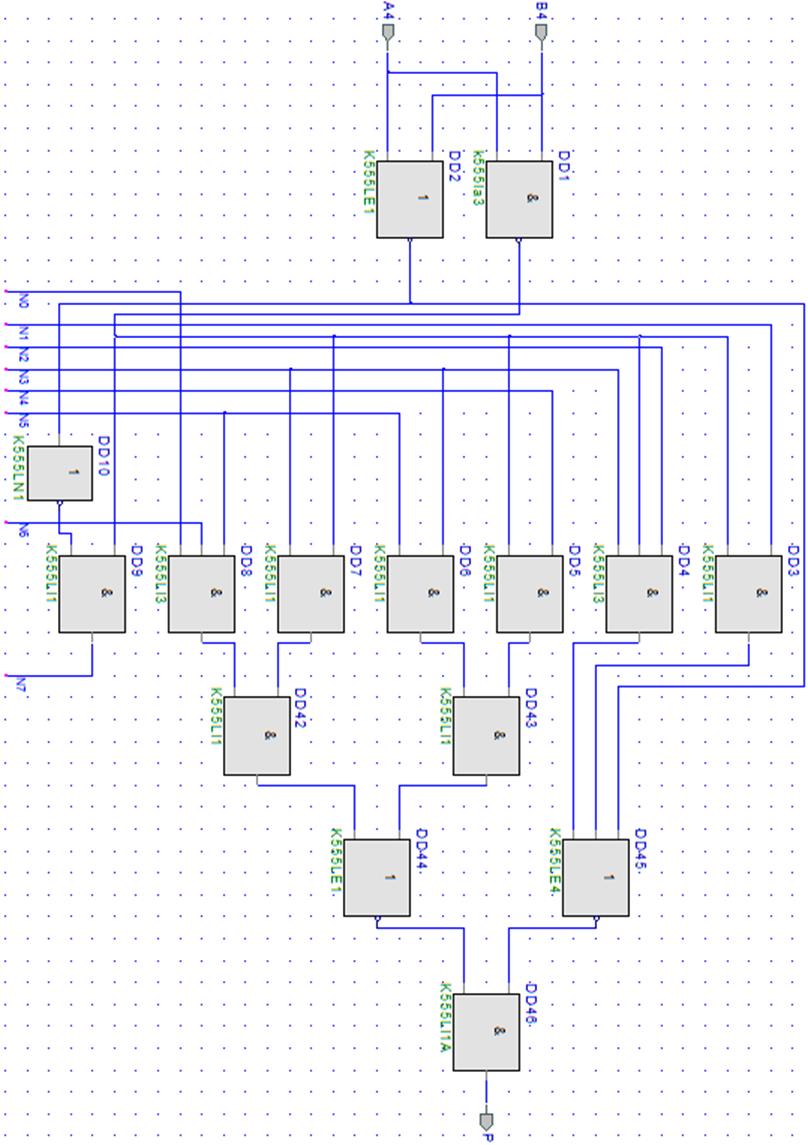

Для лучшего восприятия, принципиальная схема замещения была разбита на три страницы, которые представлены далее (стр. 29-31; рис. 30.1-30.3).

8.3. Схема верификации иерархического символа, поддерживаемого схемой

замещения.

Рис. 31. Схема верификации иерархического символа.

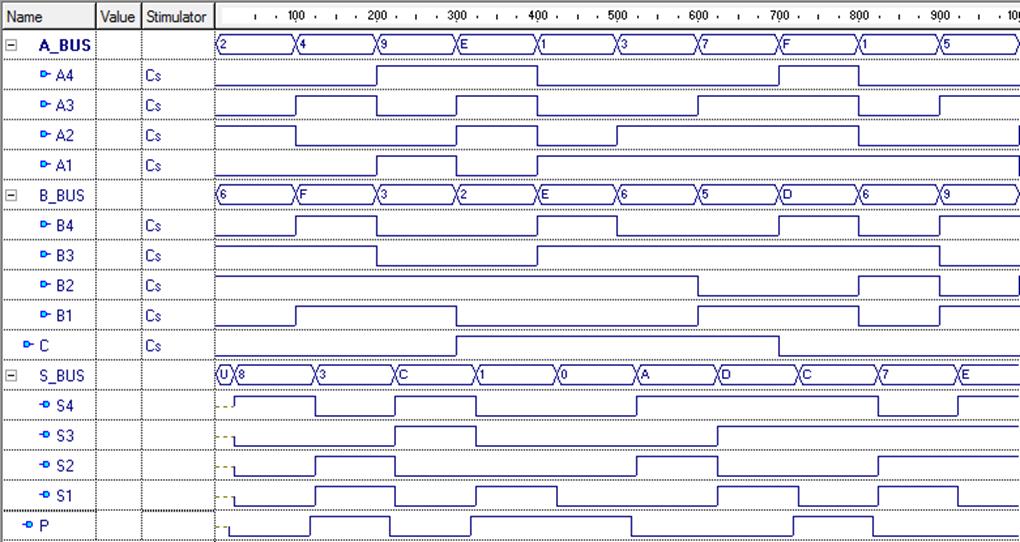

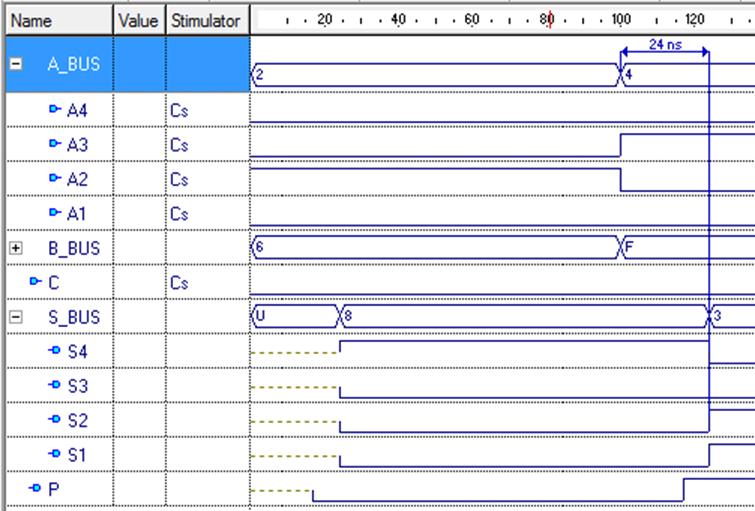

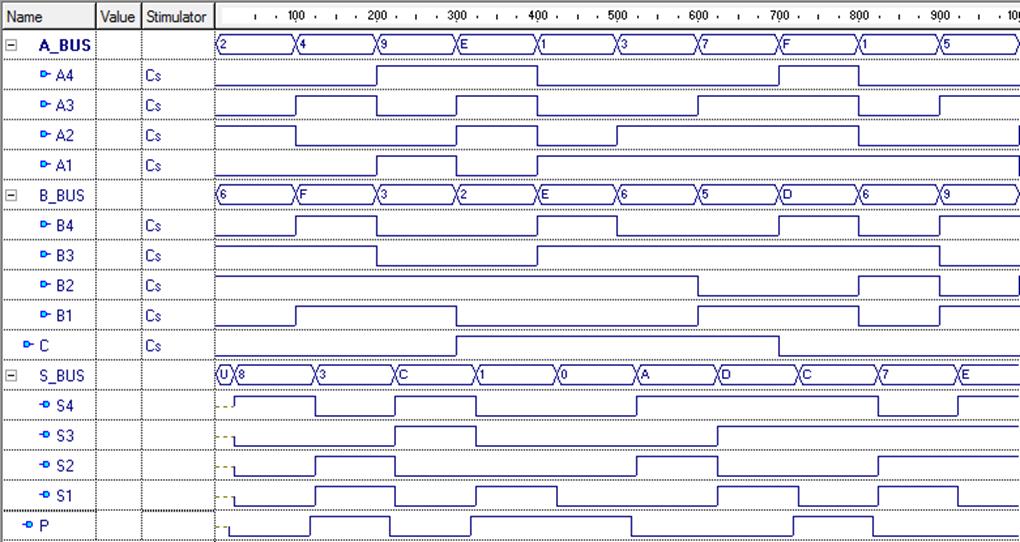

Рис. 32. Результаты моделирования узла.

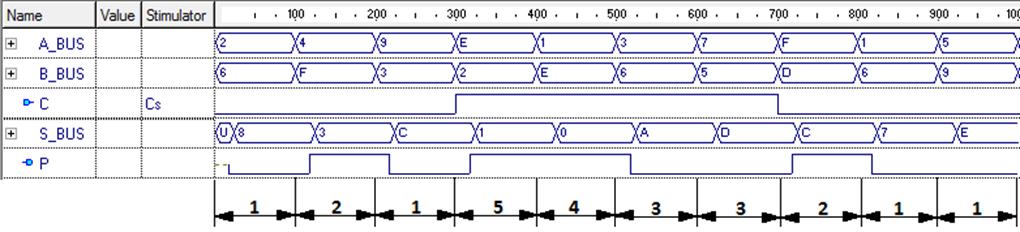

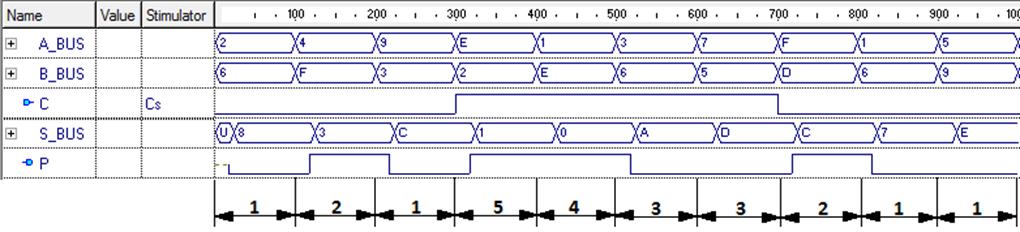

Для наглядного представления временных диаграмм и их анализа, оставим только шинные сигналы и сигналы С, Р (рис. 33).

Рис. 33. Результаты моделирования узла.

Пояснения к временным диаграммам моделирования узла:

режим №1 – суммирование без переносов (входного и выходного);

режим №2 – суммирование с формированием выходного переноса P;

режим №3 – входной перенос C увеличивает результат на единицу;

режим №4 – входной перенос увеличивает результат на единицу, что вызывает переполнение и

формирует выходной перенос;

режим №5 – переполнение при суммирование уже сформировало выходной перенос, входной

перенос лишь увеличивает значение суммы на единицу.

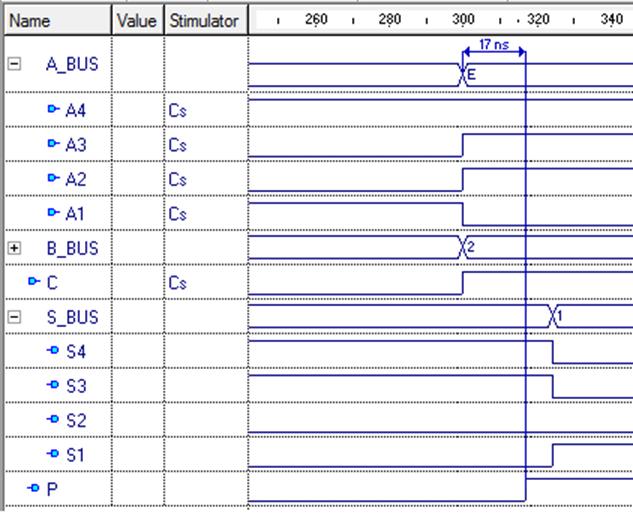

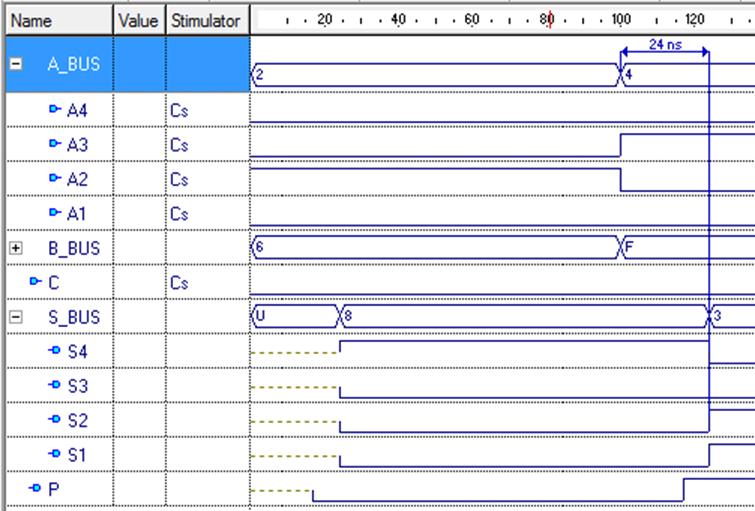

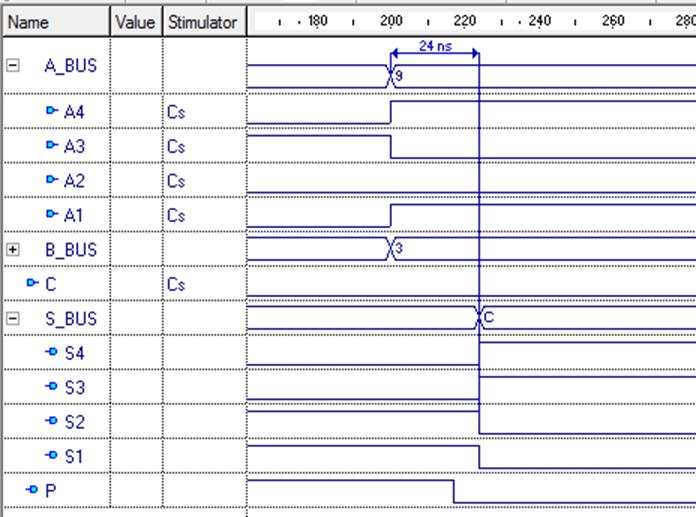

Перейдем к контролю временных соотношений в схеме (рис. 34-37).

|

Рис. 34. Время задержки распространения сигнала при включении:

Входы А,В – выход S - 24нс.

Рис. 35. Время задержки распространения сигнала при выключении:

Входы А,В – выход S - 24нс.

Рис. 36. Время задержки распространения сигнала при включении:

Вход C – выход P - 17нс.

Рис. 37. Время задержки распространения сигнала при выключении:

Вход C – выход P - 17нс.

Исходя из результатов эксперимента, можно прийти к выводу, что узел работает корректно. Все задержки, показанные на временных диаграммах совпадают с табличными, что является подтверждением правильности их имитации.

Поведенческая модель узла приведена на стр. 23.

Рис. 38. Схема верификации узла с подключенной VHDL-моделью (HS2).

Рис. 39. Временные диаграммы моделирования VHDL-модели узла (HS2).

Для наглядного представления временных диаграмм и их анализа, оставим только шинные сигналы и сигналы С, Р (рис. 40).

Рис. 40. Временные диаграммы моделирования VHDL-модели узла (HS2).

Пояснения к временным диаграммам моделирования узла:

режим №1 – суммирование без переносов (входного и выходного);

режим №2 – суммирование с формированием выходного переноса P;

режим №3 – входной перенос C увеличивает результат на единицу;

режим №4 – входной перенос увеличивает результат на единицу, что вызывает переполнение и

формирует выходной перенос;

режим №5 – переполнение при суммирование уже сформировало выходной перенос, входной

перенос лишь увеличивает значение суммы на единицу.

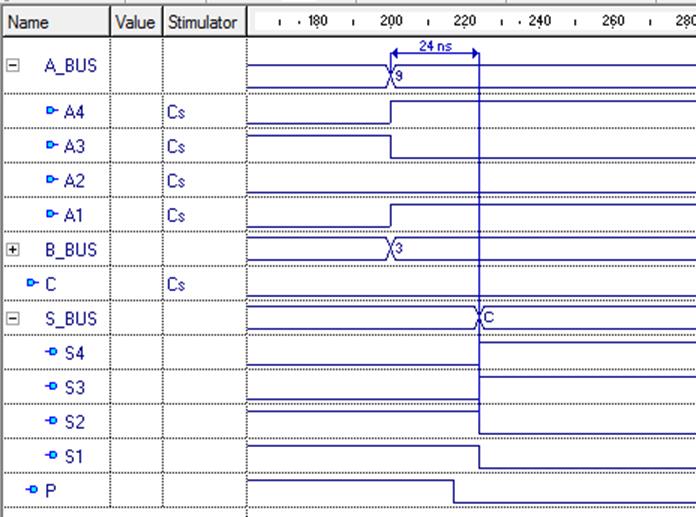

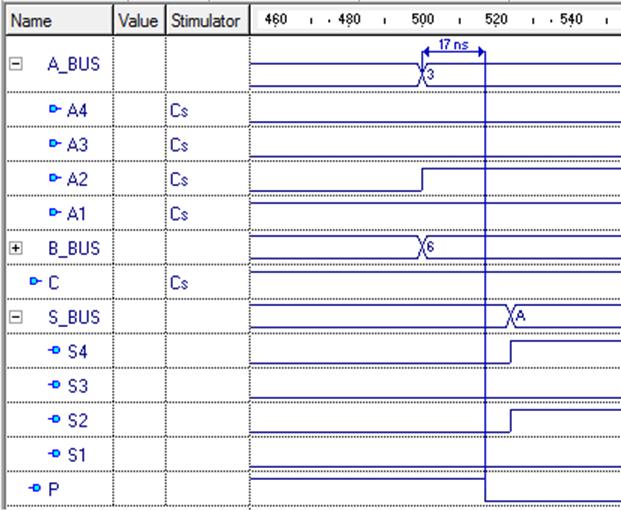

Исходя из результатов эксперимента, VHDL-модель работает корректно. Перейдем к контролю временных соотношений в VHDL-модели (рис. 41-44).

|

Рис. 41. Время задержки распространения сигнала при включении:

Входы А,В – выход S - 24нс.

Рис. 42. Время задержки распространения сигнала при выключении:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.