Оглавление

1.Постановка задачи. 2

2. Условное графическое обозначение (УГО) моделируемого узла. 2

3. Таблица назначения выводов. 2

4. Логическая таблица режимов работы. 3 5. Таблица реальных задержек. 3

6 Описание работы моделируемого узла. 3

7. Моделирование узла 555КП5 в оболочке DesignLab 8.0 4

7.1. Условное графическое изображение моделируемого узла в виде иерархического символа. 4

7.2. Схема замещения моделируемого узла. 5

10. Выводы: 22

11. Литература: 23

12.Приложение 24

1. Постановка задачи

Создать структурную и поведенческую модель мультиплексора КП 5 (или его зарубежного аналога) на языках SPICE, DSL, VHDL и SimCode в пакетах DesignLab 8, OrCAD 9.1, Active-HDL 6.1 или PCAD 2002. Также провести имитационные эксперименты с разработанным узлом, целью которых является подтверждение работоспособности узла и соответствие его временных задержек требуемым.

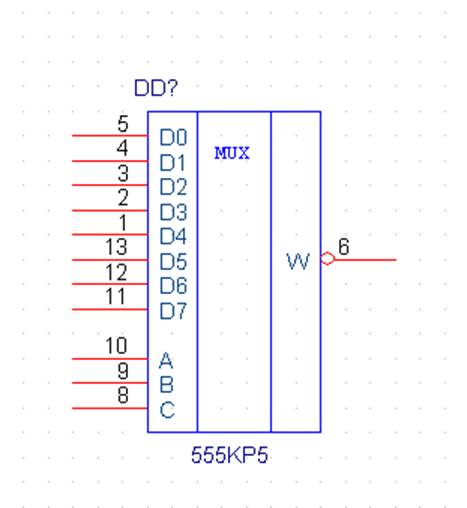

2.Условное графическое обозначение (УГО) моделируемого узла.

Рис 1. УГО микросхемы 555КП5

3. Таблица назначения выводов.[1]

Таблица1. Назначение выводов микросхемы КП5

|

№ ввода /вывода |

Обозначение входа/выхода |

Назначение |

Функции |

|

1,2,3,4,5, 11,12,13 |

D0…D7 |

входы данных |

На эти входы(входные линии) поступают данные, далее в процессе мультиплексирования, данные с одного из входов поступят на выход W. |

|

8,9,10 |

A,B,C |

адресные входы |

На эти входы поступают сигналы в соответствии с комбинацией которых, определяется с какой входной линии (D0…D7) данные поступают на выход W. |

|

6 |

W |

Выход |

Выход инверсный. На этот выход поступают инвертированные данные с одной из входной линии(D0…D7). |

|

7 |

GND |

«Земля» |

|

|

14 |

PWR(+5V) |

«Питание» |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.