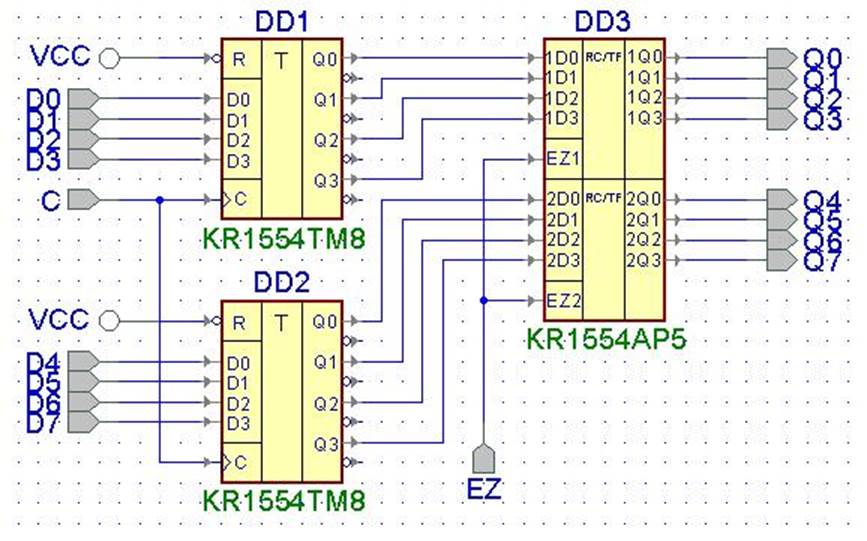

Рис.39 Схема замещения моделируемого узла

5.3. Поведенческая VHDL-модель моделируемого узла

Поведенческая модель моделируемого узла была разработана при моделировании узла в пакете OrCAD_9.1 и приведена в пункте 4.4. В пакет Active-HDL_6.1 данная поведенческая VHDL-модель была перенесена без изменений.

5.4. Результаты моделирования в пакете Active-HDL_6.1

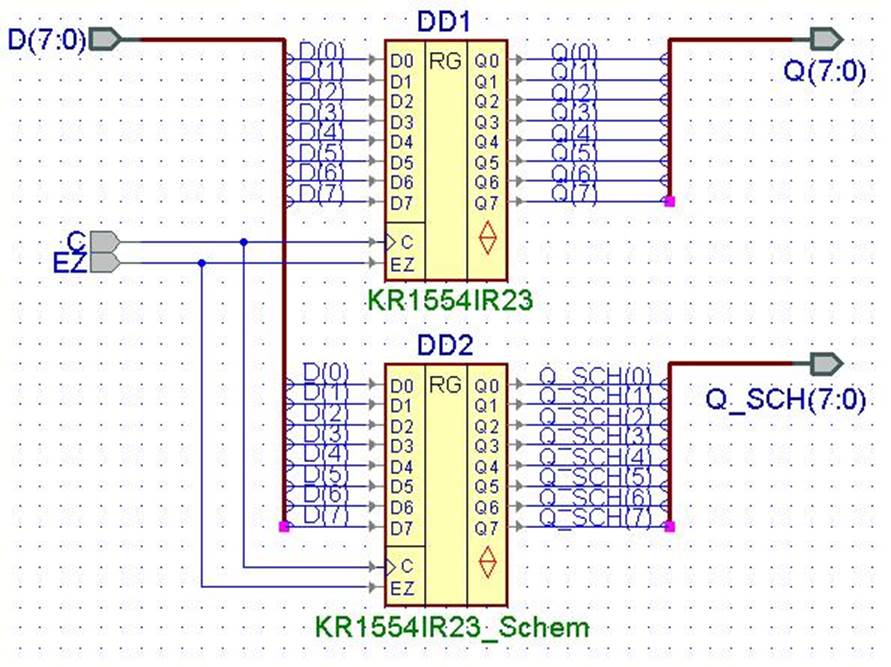

На рисунке 40 приведена схема верификации разработанных моделей.

Испытания проводятся для максимальных задержек. Сравнение производится с максимальными задержками указанными в таблице 3 для входной емкости Сl=50пФ и температуры окружающей среды T=25ºC. Напряжение питания VCC=5В.

Рис.40 Схема верификации разработанных моделей

На представленной схеме иерархический символ KR1554IR23 имеет внутреннее описание представленное поведенческою VHDL-моделью, а KR1554IR23_Schem принципиальной схемой замещения.

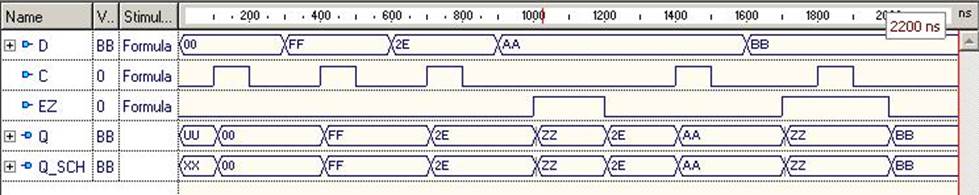

На рисунке 41 приведена диаграмма результата моделирования разработанных моделей по которой видно, что работа обеих моделей идентична, за исключением отрезка времени до поступления первого фронта синхросигнала.

До поступления первого синхросигнала триггеры, входящие в схему имеют случайное состояние. В двух разных реализациях и результаты имитации этого состояния получилось разным. В случаи с поведенческой VHDL-моделью, начальное состояние неизвестно (U), в то время как модель представленная принципиальной схемой замещения имеет на выходе любое значение (X).

Так как схема замещения построена на иерархических символах, внутреннее описание которых представлено поведенческими VHDL-моделями, то различие вызвано особенностью моделирования разных типов иерархических символов.

Рис.41 Диаграмма моделирования разработанных моделей

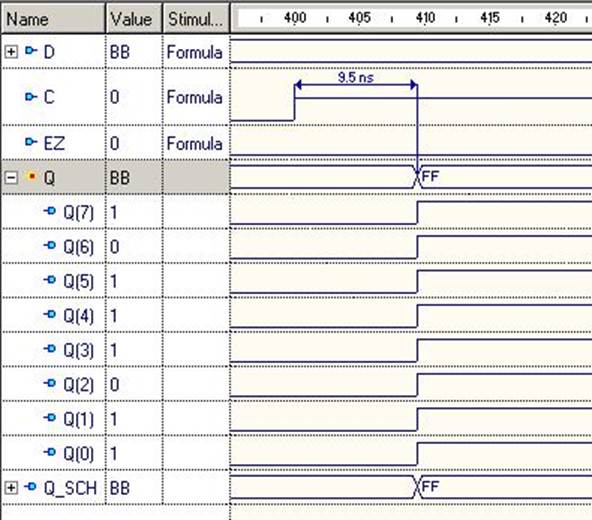

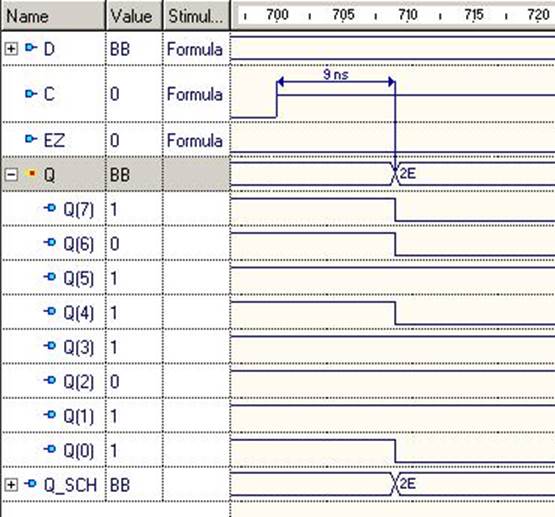

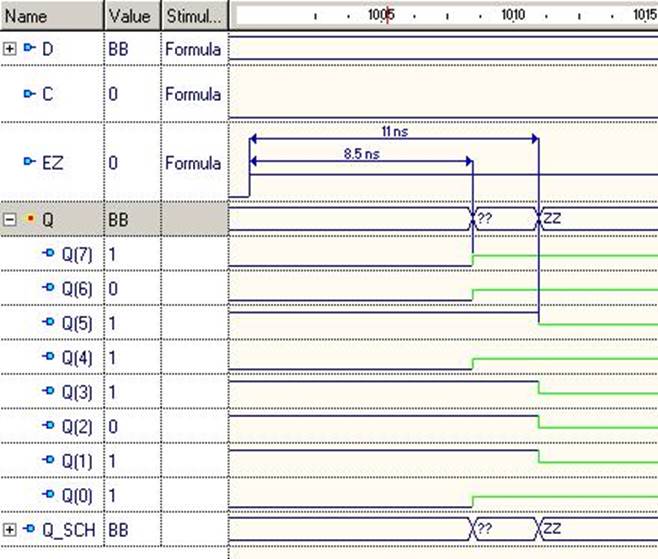

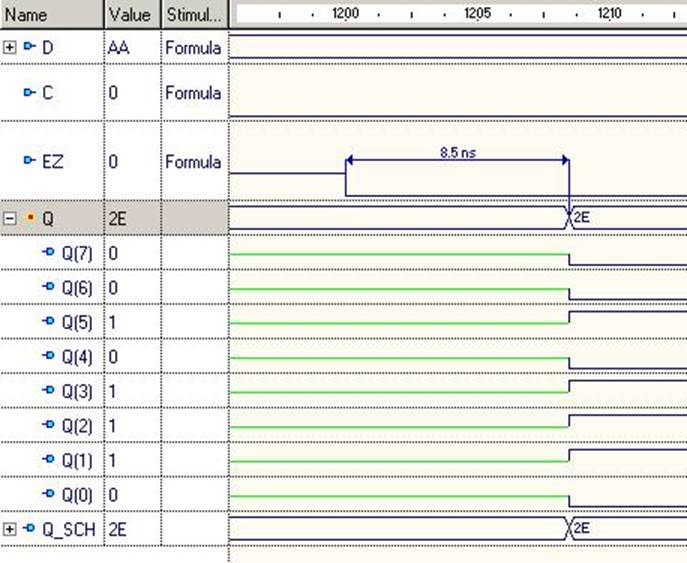

На рисунках 42-45 приведены диаграммы, на которых измерены временные задержки воспроизводимые моделями.

Рис.42 Время задержки распространения сигнала при включении от входа С к выходам Q

Рис.43 Время задержки распространения сигнала при выключении от входа С к выходам Q

Рис.44 Задержки распространения при переключении выходов в высокоимпедансное состояние

Рис.44 Задержка распространения при переходе из высокоимпедансного состояния.

Проведенные измерения показывают, что модель адекватно воспроизводит все временные задержки прохождения сигналов заданные в соответствии с динамическими характеристиками реальной ИМС.

Выводы

В данной курсовой работе были использованы три пакета (среды) моделирования: DesignLab_8, OrCAD_9.1 и Active-HDL_6.1. В результате полученного опыта можно провести некоторый сравнительный анализ рабочего инструмента.

В первую очередь необходимо отметить, вышеуказанные САПР разрабатывались в разное время, что существенно сказывается на качестве их реализации.

Первым был DesignLab_8, который по своим функциональным возможностям не уступает OrCAD_9.1, однако неоправданно неудобен с точки зрения эксплуатации. Малейшее отступление от задуманного разработчиками алгоритма в DesignLab_8 беспощадно карается, в результате чего бесполезно потраченное время и нервы на «войны» с пакетом ничем не окупаются. Также много неудобства доставляет структура окон пакета, когда каждая маленькая подпрограмма стремится к суверенитету!

Реализация работы в OrCAD_9.1 с точки зрения перечисленных недостатков, гораздо удачнее. Этого и следовало ожидать от пакета основой которого стал DesignLab_8.

Active-HDL_6.1 является самой новой разработкой и выгодно отличается удобством организации работы, при котором разработчики избавили пользователя от рутинной работы по подключению к проекту различных библиотек, файлов с описанием входных воздействий и т.п. мелочей.

Являясь более новыми разработками пакеты OrCAD_9.1 и Active-HDL_6.1 включают поддержку языка VHDL, в отличие от DesignLab_8, в котором используется морально устарелый DSL.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.