IF D5='1' THEN Q5<='1' AFTER 9.5ns; ELSE Q5<='0' AFTER 9ns; END IF;

IF D6='1' THEN Q6<='1' AFTER 9.5ns; ELSE Q6<='0' AFTER 9ns; END IF;

IF D7='1' THEN Q7<='1' AFTER 9.5ns; ELSE Q7<='0' AFTER 9ns; END IF;

END IF;

END IF;

IF EZ='1' AND EZ'EVENT

THEN—-Если сигнал разрешения принял значения логической единицы, то выходные

--буферы должны быть переведены в третье состояние, при этом задержка

--переключения зависит от исходного состояния выходов

IF iQ0='1' THEN Q0<='Z' AFTER 11ns; ELSE Q0<='Z' AFTER 8.5ns; END IF;

IF iQ1='1' THEN Q1<='Z' AFTER 11ns; ELSE Q1<='Z' AFTER 8.5ns; END IF;

IF iQ2='1' THEN Q2<='Z' AFTER 11ns; ELSE Q2<='Z' AFTER 8.5ns; END IF;

IF iQ3='1' THEN Q3<='Z' AFTER 11ns; ELSE Q3<='Z' AFTER 8.5ns; END IF;

IF iQ4='1' THEN Q4<='Z' AFTER 11ns; ELSE Q4<='Z' AFTER 8.5ns; END IF;

IF iQ5='1' THEN Q5<='Z' AFTER 11ns; ELSE Q5<='Z' AFTER 8.5ns; END IF;

IF iQ6='1' THEN Q6<='Z' AFTER 11ns; ELSE Q6<='Z' AFTER 8.5ns; END IF;

IF iQ7='1' THEN Q7<='Z' AFTER 11ns; ELSE Q7<='Z' AFTER 8.5ns; END IF;

END IF;

IF EZ='0' AND EZ'EVENT

THEN—-Если сигнал запрета выходных буферов был снят, то спустя задержку

--распространения на выходах появятся данные, хранимые в триггерах

Q0<=iQ0 AFTER 8.5ns;

Q1<=iQ1 AFTER 8.5ns;

Q2<=iQ2 AFTER 8.5ns;

Q3<=iQ3 AFTER 8.5ns;

Q4<=iQ4 AFTER 8.5ns;

Q5<=iQ5 AFTER 8.5ns;

Q6<=iQ6 AFTER 8.5ns;

Q7<=iQ7 AFTER 8.5ns;

END IF;

END PROCESS;

END model;

4.5. Тестирование разработанной поведенческой VHDL-модели

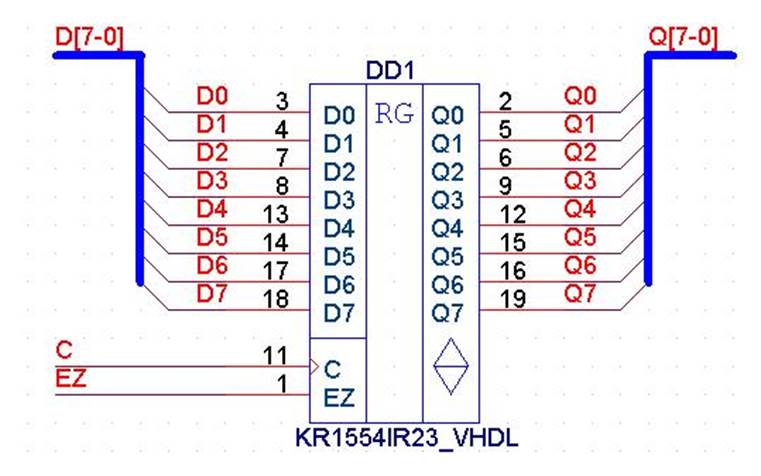

На рисунке 31 приведена схема верификации разработанной поведенческой VHDL-модели узла.

Рис.31 Схема верификации иерархического символа с внутренним описанием в виде поведенческой VHDL-модели

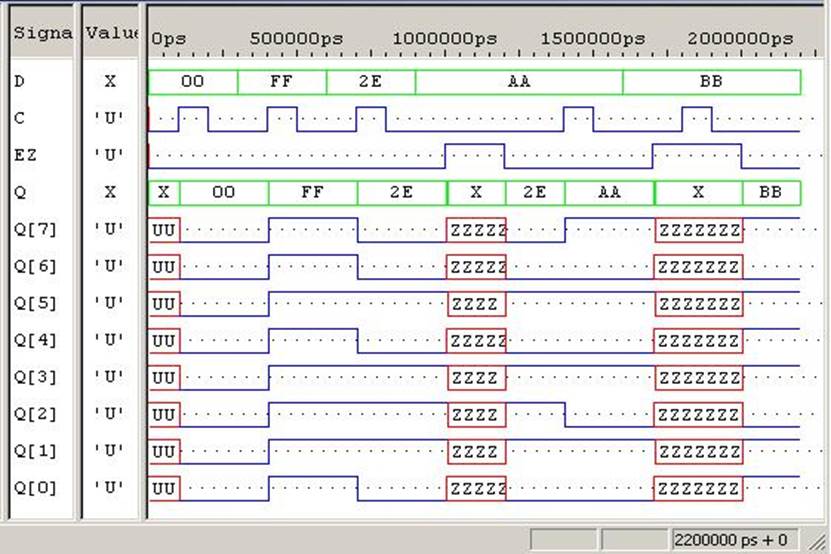

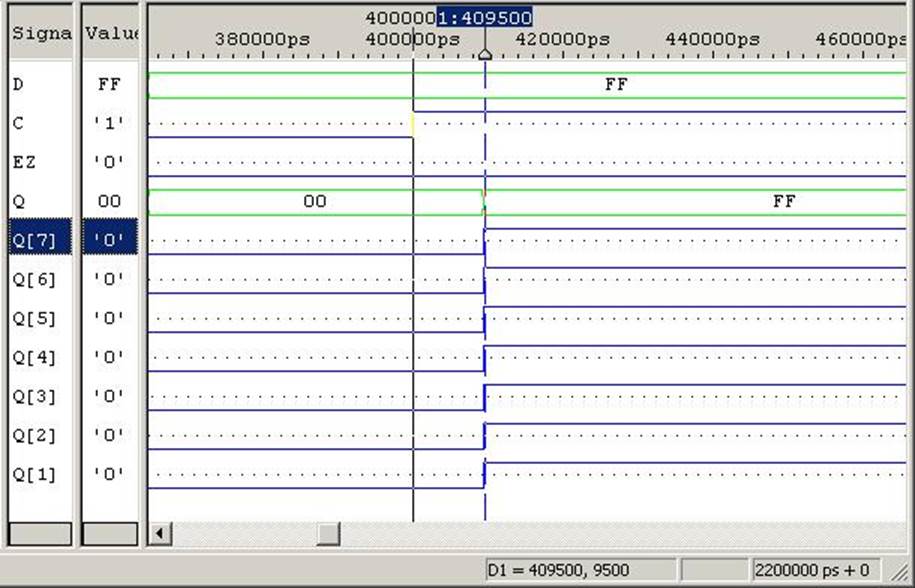

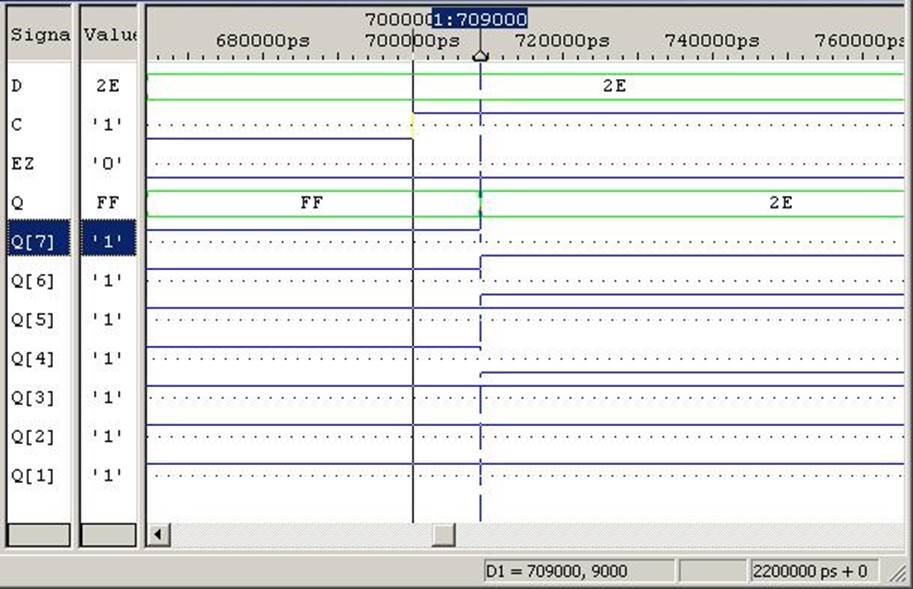

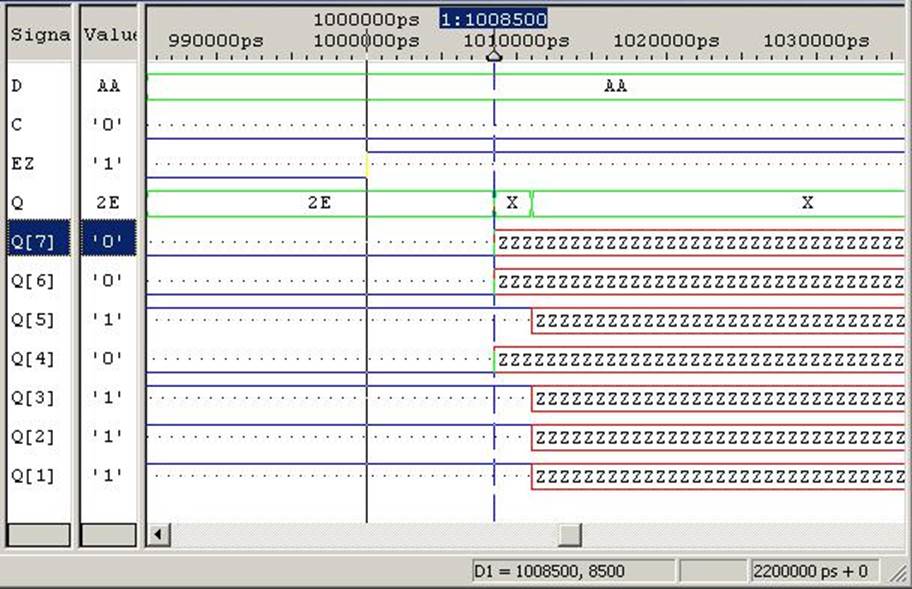

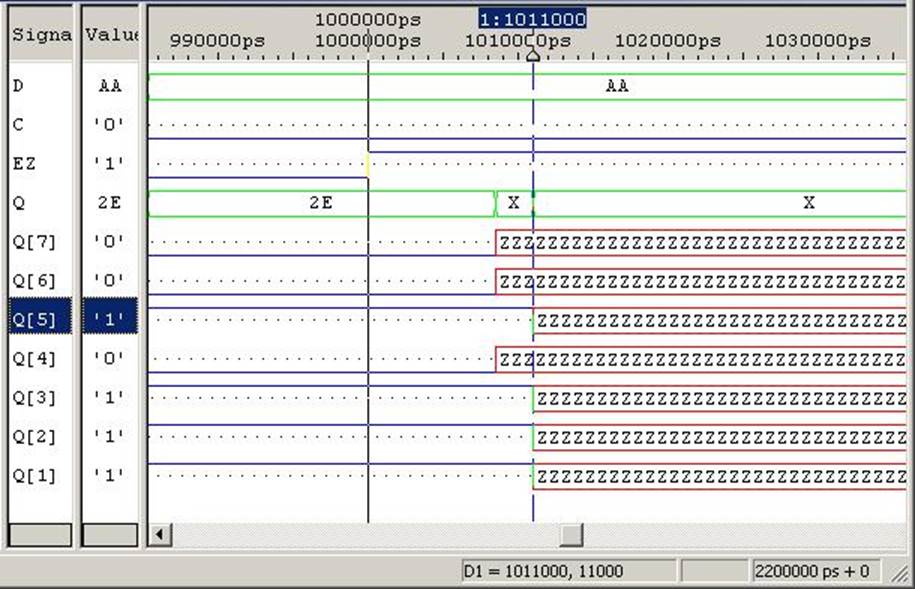

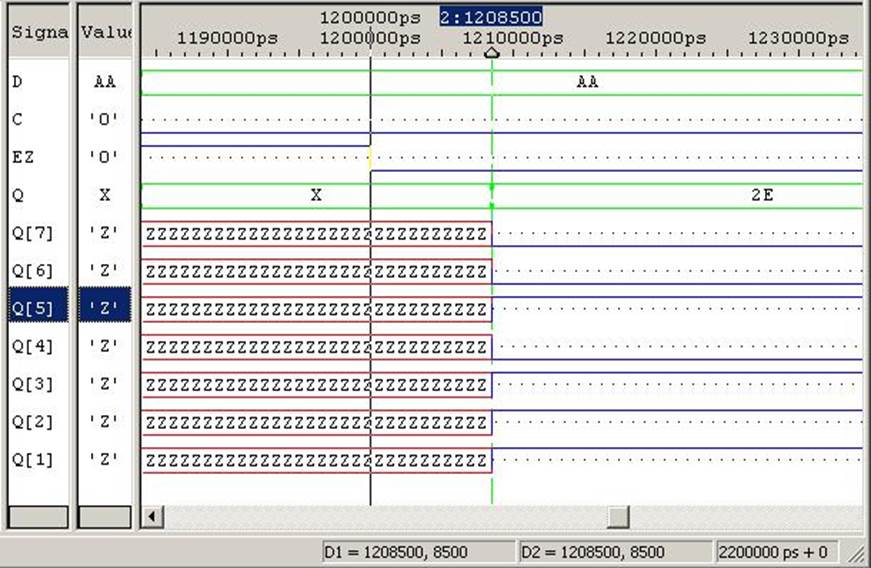

На рисунках 32 – 37 приведены диаграммы тестирования разработанной модели с указанием задержек заложенных в нее.

Рис.32 Диаграмма тестирования работы иерархического символа

Рис.33 Время задержки распространения сигнала при включении от входа С к выходам Q

Рис.34 Время задержки распространения сигнала при выключении от входа С к выходам Q

Рис.35 Время задержки распространения сигнала при переходе из состояния логического нуля в состояние высокого импеданса от входа EZ к выходам Q

Рис.36 Время задержки распространения сигнала при переходе из состояния логической единицы в состояние высокого импеданса от входа EZ к выходам Q

Рис.37 Время задержки распространения сигнала при переходе из состояния высокого импеданса в состояние высокого или низкого логического уровня от входа EZ к выходам Q

Проведенные измерения показывают, что модель адекватно воспроизводит все временные задержки прохождения сигналов заданные в соответствии с динамическими характеристиками реальной ИМС.

5. Моделирование узла в пакете ACTIVE-HDL_6

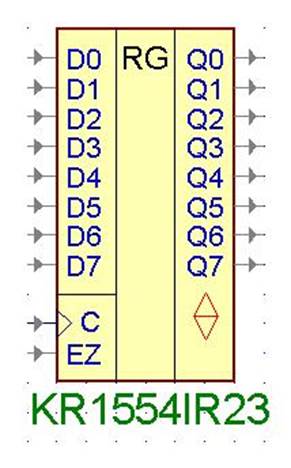

5.1. Условное графическое обозначение моделируемо узла

На рисунке 38 приведено УГО моделируемого узла в пакете Active-HDL_6.1. На приведенном рисунке видно, что элемент не имеет цоколевки. Причина – пакет Active -HDL разрабатывался не для создания схем разводки печатных плат, а с ориентацией на синтез “прошивок” для программируемой логики, при создании которой такая информация, как цоколевка выходов является бесполезной.

Рис.38 УГО моделируемого узла в пакете Active-HDL_6.1

В результате работы были созданы две модели узла: с внутренним описанием в виде принципиальной схемы замещения и поведенческим описанием на языке VHDL.

5.2. Схема замещения моделируемого узла

На рисунке 39 приведена схема замещения моделируемого узла. Схема замещения выполнена на элементной базе серии КР1554: КР1554ТМ8 – четыре D-триггера с общим выводом асинхронного сброса и синхронизации; КР1554АП5 – два четырехразрядных формирователя (буфера) с тремя состояниями на выходе. Поведенческие модели элементов, входящих в состав схемы взяты из стандартной библиотеки пакета OrCAD_9 (с небольшой доработкой).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.