+ ;разрешенное

+ CHANGED(iEZ,0) & TRN_LZ, DELAY(-1, 1ns, 8.5ns), ;Задержка переключения из 0 в Z

+ CHANGED(iEZ,0) & TRN_HZ, DELAY(-1,1ns, 11ns), ;Задержка переключения из 1 в Z

+ Cfront & TRN_LH, DELAY(-1, 1ns, 9.5ns), ;Задержка от входа C до выходов Q при включении

+ Cfront & TRN_HL, DELAY(-1, 1ns, 9ns) , ;Задержка от входа C до выходов Q при выключении

+ DELAY(-1, 2ns, 2ns) ) } ;Для событий (которых нет)

*

U4 CONSTRAINT(9) ;Начало блока контроля режимных параметров, контролируются 9 сигналов

+ DPWR DGND ;Контакты питания и земли

+C D0 D1 D2 D3 D4 D5 D6 D7 ;Контролируемые сигналы

+IO_STD

+ WIDTH: ;Контроль

+ NODE = C ;Контроль сигнала C

+ MIN_LO = 5ns ;Минимальный интервал логического нуля на входе тактового сигнала

+ MIN_HI = 5ns ;Минимальный интервал логической единицы на входе тактового сигнала

+

+ SETUP_HOLD: ;Контроль времени предустановки и удержания

+ DATA(8) = D0 D1 D2 D3 D4 D5 D6 D7 ;Всего по восьми входам

+ CLOCK LH = C ;Относительно тактового сигнала С

+ SETUPTIME = 4ns ;Минимальное время предустановки входов D относительно C

+ HOLDTIME = 1ns ;Минимальное время удержания входов D относительно С

.ends ;Конец макромодели

.MODEL D_KR1554IR23_MM UGATE() ;Динамическая модель с нулевыми задержками

3.8. Тестирование макромодели моделируемого узла

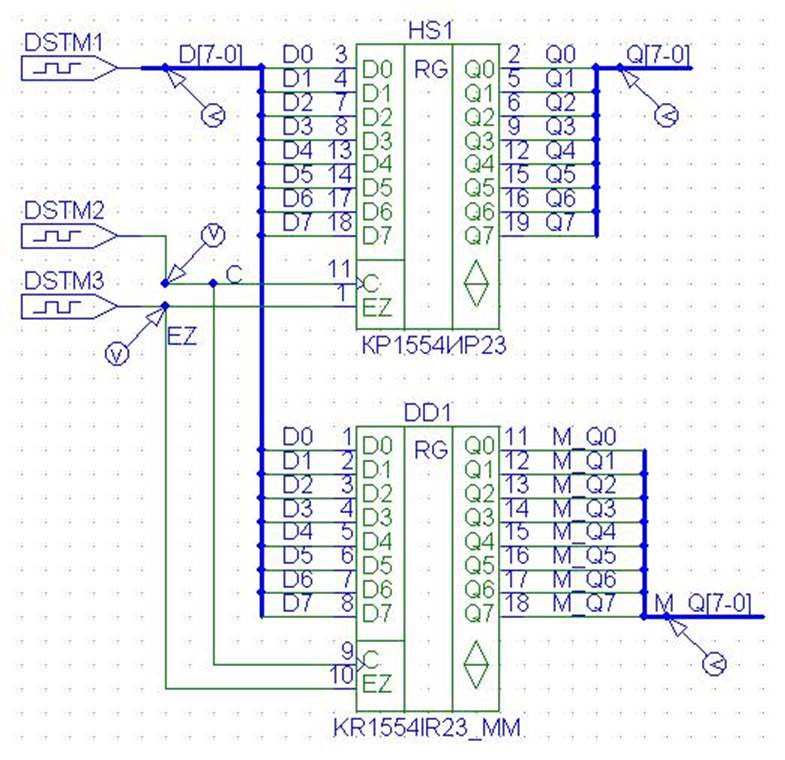

На рисунке 20 представлена схема верификации разработанной модели (KR1554IR23_MM), функциональное описание которой приведено в предыдущем пункте, а на рисунке 21 приведен результат проведенного эксперимента (диаграмма).

Рис.20 Схема верификации разработанных моделей

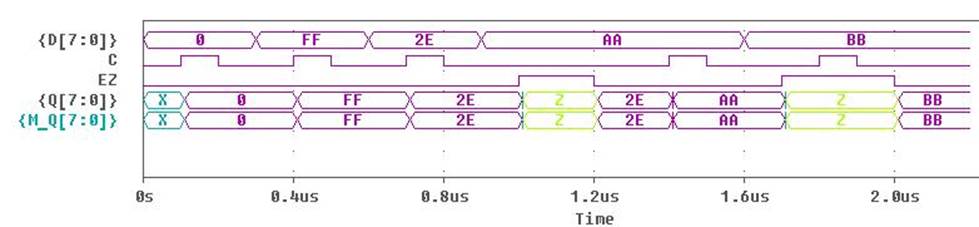

Рис.21 Результат эксперимента над разработанными моделями узла

По приведенной диаграмме видно, что обе разработанные модели узла работают идентично и воспроизводят все режимы работы реальной ИМС с соответствующими временными задержками.

4. Моделирование узла в пакете OrCAD_9.1

4.1. Условное графическое обозначение моделируемого узла

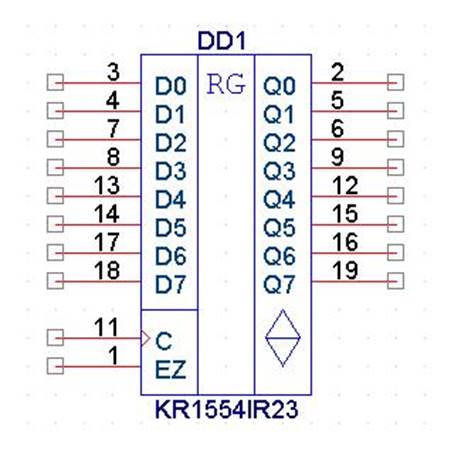

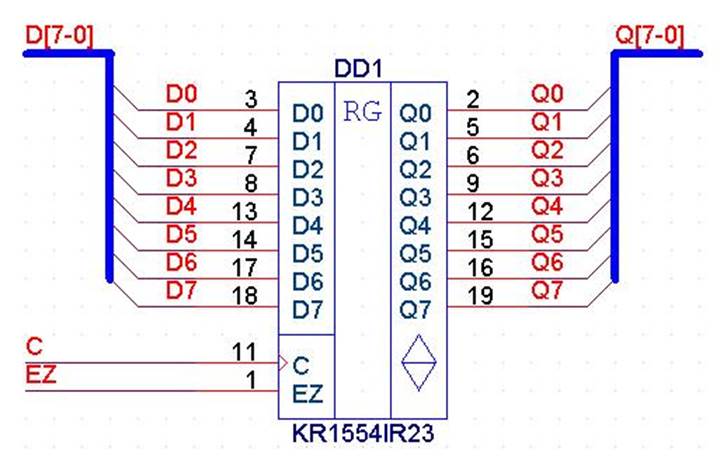

На рисунке 22 приведено УГО для пакета OrCAD_9.1.

Рис.22 УГО моделируемого узла в пакете OrCAD_9.1

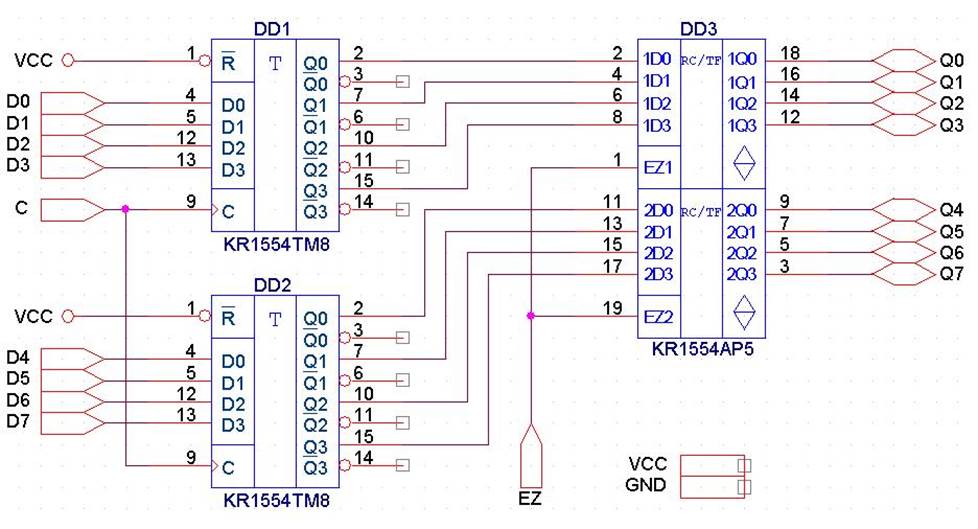

4.2. Схема замещения моделируемого узла

Схема замещения выполнена на элементной базе серии КР1554: КР1554ТМ8 – четыре D-триггера с общим выводом асинхронного сброса и синхронизации; КР1554АП5 – два четырехразрядных формирователя (буфера) с тремя состояниями на выходе. На рисунке 23 представлена полученная схема замещения.

Рис.23 Схема замещения иерархического символа

Динамические характеристики элементов подобраны (изменены) так, чтобы в сумме давали задержки соответствующие реальным задержкам моделируемого узла.

Необходимо отметить, что стандартная модель библиотеки OrCAD - orcad_tsb (модель буфера с выходами на три состояния) не позволяет моделировать переключения выходов из состояния 1 -> Z и 0 -> Z с разными задержками. То есть можно моделировать лишь событие $ -> Z (задержка переключения выходов в третье состояние), что приводит к невозможности показать различие между tphz = 11ns и tplz = 8.5 ns.

Поэтому стандартная модель буфера была переделана с исправлением этого «дефекта».

4.3. Результаты моделирования узла в пакете OrCAD_9.1

На рисунке 24 представлена схема тестирования разработанной модели. Испытания проводятся для максимальных задержек. Сравнение производится с максимальными задержками, указанными в таблице 3 для входной емкости Сl=50пФ и температуры окружающей среды T=25ºC. Напряжение питания VCC=5В.

Рис.24 Схема верификации иерархического символа с внутренним описанием в виде принципиальной схемы замещения

Входные воздействия заданы так, чтобы показать все возможные режимы работы узла и соответствующие этим режимам задержки. На рисунке 25 представлена тестовая диаграмма.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.