2 :: 4;

3 :: 8;

END TRUTH_TABLE;

END DC2_4;

PROCEDURE DC3_8 (

INPUT D1, D2, D3 ;

OUTPUT O0, O1, O2, O3, O4, O5, O6, O7 ;);

TRUTH_TABLE

[D3..D1] :: [O7..O0];

0 :: 1;

1 :: 2;

2 :: 4;

3 :: 8;

4 :: 16;

5 :: 32;

6 :: 64;

7 :: 128;

END TRUTH_TABLE; Рис 13

END DC3_8;

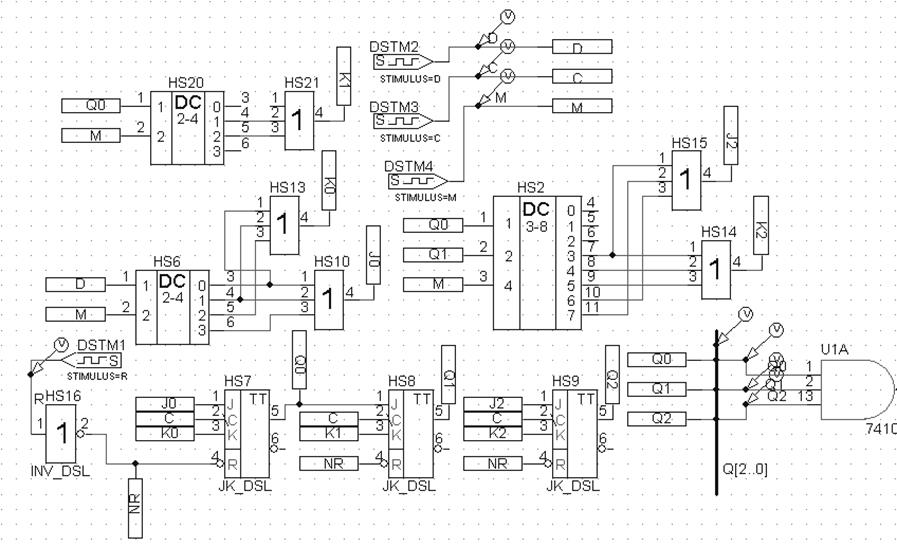

10. Синтез комбинационной части автомата на ПЗУ

Суть следующая: в ПЗУ зашиваются таблицы 5, 6, 7, а на адресные входы подаются переменные, от которых зависят функции возбуждения триггеров. Я думаю, здесь не стоит много говорить, потому что и так все понятно…

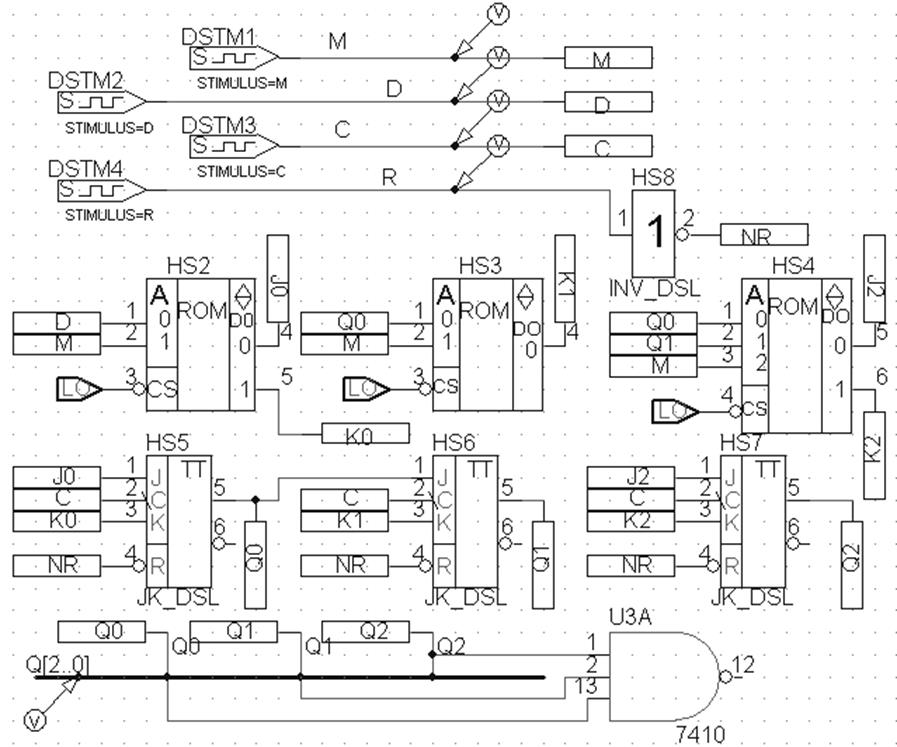

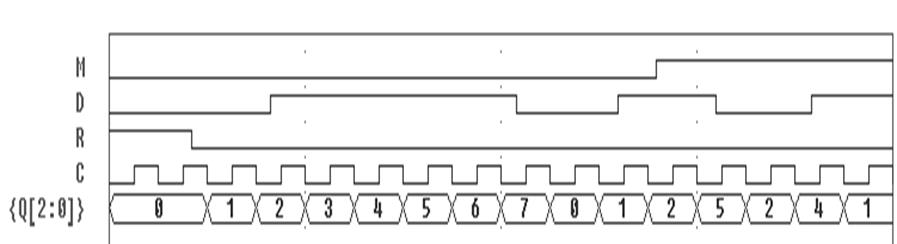

На рис. 14 приведена схема верификации, на рис. 15 результаты ее работы. Если заметить, то у элементов памяти есть вход /CS. Просто хотелось чтоб были какие-то стандарты. Ниже приведены DSL-модели памяти.

PROCEDURE ROM2 (

INPUT A0, A1, CS ;

OUTPUT DO0, DO1 ENABLED_BY /CS;

);

TRUTH_TABLE

[A1,A0] :: DO0, DO1;

0 :: 1, 1;

1 :: 1, 1;

2 :: 0, 1;

3 :: 1, 0;

END TRUTH_TABLE;

END ROM2;

PROCEDURE ROM2_1 (

INPUT A0, A1, CS ;

OUTPUT DO0 ENABLED_BY /CS;

);

TRUTH_TABLE

[A1,A0] :: DO0;

0 :: 0;

1 :: 1;

2 :: 1;

3 :: 0;

END TRUTH_TABLE;

END ROM2_1;

PROCEDURE ROM3 (

INPUT A0, A1, A2, CS ;

OUTPUT DO0, DO1 ENABLED_BY /CS;

);

TRUTH_TABLE

[A2..A0] :: DO0, DO1;

0 :: 0, 0;

1 :: 0, 0;

2 :: 0, 0;

3 :: 1, 1;

4 :: 0, 1;

5 :: 0, 1;

6 :: 1, 0;

7 :: 1, 0;

END TRUTH_TABLE;

END ROM3;

УГО элементов очень хорошо различимы на рис. 14.

Рис. 14

Рис. 15

Выводы, личные впечатления

В ходе выполнения работы были изучены методы синтеза и проектирования автоматов с памятью, а в частности счетчика-регистра. Разнообразие методов задания комбинационной части для автомата очередной раз доказало, что на построение комбинационной части вентилях не самый рациональный метод. Разнообразие DSL-моделей начиная от отдельного элемента и заканчивая потоковой еще больше закрепило познания, которые накопились в ходе работы в семестре.

Работа выполнялась в пакете фирмы MicroSim Design Lab 8. В мире нет идеала, поэтому и в данном пакете с моей точки зрения есть свои прелести и недостатки.

Что мне понравилось.

Что мне не понравилось.

Это, конечно, моя точка зрения, я не могу еще полностью сравнить эти два пакета между собой, так как нет объемной работы в пакете Orcad9.1. Но одно могу сказать точно – пакет Design Lab8 оставил о себе приятное впечатление, так как и выполнение работы, проделанной в нем.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.