Блок памяти SRAM

Блок памяти SRAM

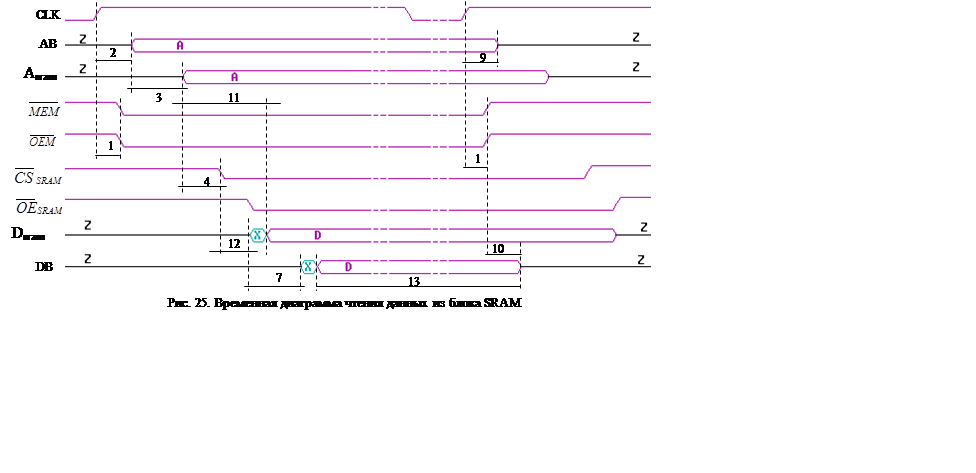

Чтение (![]() = H)

= H)

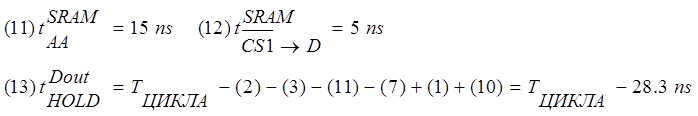

Запись

Запись

Фактически на вход данных блока SRAM будут подаваться данные весь цикл, как и на адрес, но чтобы показать достаточное время «выдержки» для успешной записи данных было принято решение, выделить «не нужное время» подачи данных и адреса на входы ИМС памяти. Кстати, это относится и к другим временным диаграммам, но на них это время не выделено (графически).

8. Разработка блока синхронизации[4,7]

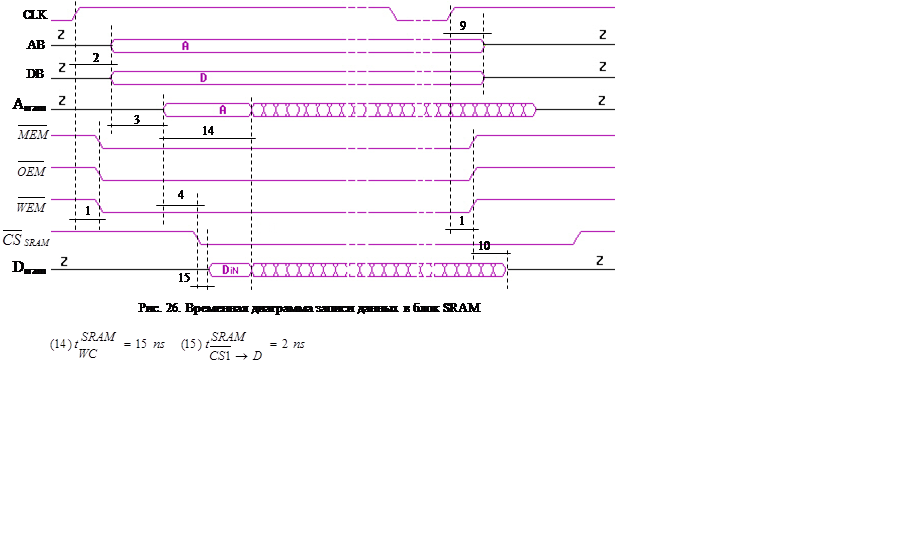

8.1 Структурное описание

Устройство синхронизации (УС) предназначается для

выработки импульсных последовательностей согласующихся по времени работу узлов

и устройств в подсистеме или системе в аппаратных средствах.

Устройство синхронизации (УС) предназначается для

выработки импульсных последовательностей согласующихся по времени работу узлов

и устройств в подсистеме или системе в аппаратных средствах.

Генератор генерирует последовательность прямоугольных импульсов с определённой частотой. Формирователь опорных сигнал (обычно используются делители частоты) преобразовывает последовательность в системные синхросигналы. Схема размножения увеличивает мощность синхросигналов. Нельзя допустить расфазировку синхросигналов, что вызовет сбои в аппаратуре. Для этого необходимо использовать ИМС размножения с очень малой расфазировкой CLK.

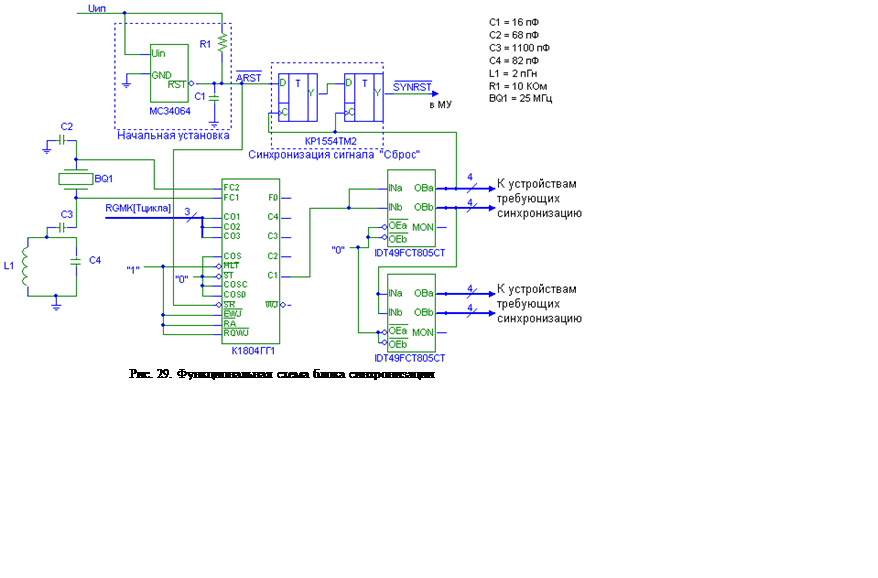

![]() В качестве

генератора, выдающего синхросигнал CLK, взята микросхема К1804ГГ1. К1804ГГ1 –

системный тактовый генератор (ТГ), предназначен для применения в составе блоков

синхронизации центральных процессоров микро-ЭВМ и других вычислительных

устройств в качестве задающего тактового генератора (ТГ).

Микросхема ТГ содержит внутренний генератор опорной синхропоследовательности:

опорная частота (до 30 МГц) задается внешним кварцевым резонатором. Данный

генератор позволяет формировать синхросигнал с различной длительностью сигнала

высокого и низкого уровней [4].

В качестве

генератора, выдающего синхросигнал CLK, взята микросхема К1804ГГ1. К1804ГГ1 –

системный тактовый генератор (ТГ), предназначен для применения в составе блоков

синхронизации центральных процессоров микро-ЭВМ и других вычислительных

устройств в качестве задающего тактового генератора (ТГ).

Микросхема ТГ содержит внутренний генератор опорной синхропоследовательности:

опорная частота (до 30 МГц) задается внешним кварцевым резонатором. Данный

генератор позволяет формировать синхросигнал с различной длительностью сигнала

высокого и низкого уровней [4].

Инструкции на формирование подаются из МУУ (поле Тцикла). Общее время цикла системы не может быть меньше T= ТЦИКЛА ОБ + 0.05* ТЦИКЛА ОБ = 149.2 + 7.46 = 156.6 нс. Соответственно, частота синхронизации не может быть больше F = 1/(156.6 * 10-9) = 6.38 МГц.

Для снижения нагрузки на выходы ИМС К1804ГГ1 и увеличения линий синхросигнала, используется схема размножения синхросигнала фирмы IDT IDT49FCT805CT.

8.2 Начальная установка

При включении питания, необходимо установить секвенсор

по нулевому адресу. Это осуществляется путем подачи сигнала “RESET” на вентели

И включённые перед вх. инструкций SEQMK. Соответственно, по этому

адресу в МПП должна хранится МК инициализации системы, т.е. все выходы RG-ов

и устройств перевести в состояние высокого импеданса, что бы ни вызвать

конфликтов на шинах, а также SEQ должен разрешить вывод данных ПНА (Iseq

= 0010 à ![]() ).

).

Схема начальной установки выполнена с применением микросхемы MC34064, фирмы MOTOROLA. Микросхема MC34064 это специализированный для микропроцессорных систем контроллер предустановки, применяемый для выработки асинхронного сигнала RESET.

|

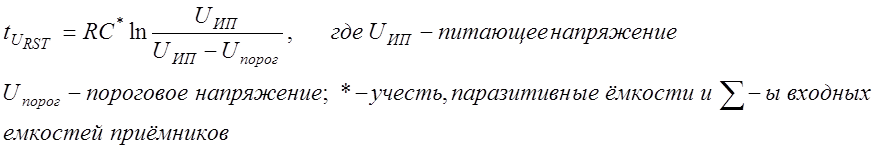

Производитель не рекомендует делать время начальной установки схемы менее 500нс. Исходя из этого и применив формулу расчета длительности сигнала RESET, находим значение емкости С и резистора R. R = 10 КОм, С = 16.7 пФ. При этих значениях емкости и сопротивления, длительности сигнала RESET составит ³ 500 нс (»550 нс). Функциональная схема сброса показан на рис.29.

Т.О. получен асинхронный сигнал сброса (

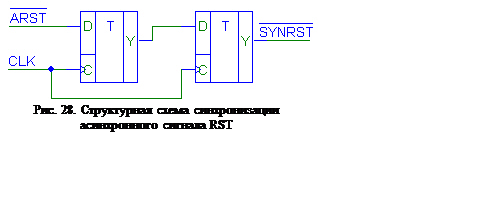

Т.О. получен асинхронный сигнал сброса (![]() ). Теперь его необходимо синхронизовать, делается это

по схеме показанной на рис. 28.

). Теперь его необходимо синхронизовать, делается это

по схеме показанной на рис. 28.

8.3 Функциональная схема блока синхронизации

Из выше сказанного можно составить функциональную схему блока

синхронизации рис. 29.

В

качестве D- триггеров, для синхронизации асинхронного

сигнала сброса, взята отечественная ИМС КР1554ТМ2. ИМС содержит 2-а триггера

типа D (![]() ).

ИМС размножения синхросигнала, как и было сказано выше, фирмы IDT IDT49FCT805CT (

).

ИМС размножения синхросигнала, как и было сказано выше, фирмы IDT IDT49FCT805CT (![]() ).

).

Для целесообразности реализации микропрограммного управления длительностью цикла, было принято решение использовать внешний резонатор с частотой = 25 МГц, т.е. Тмикротакта = 40 нс. Исходя из этого можно сказать, что

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.