|

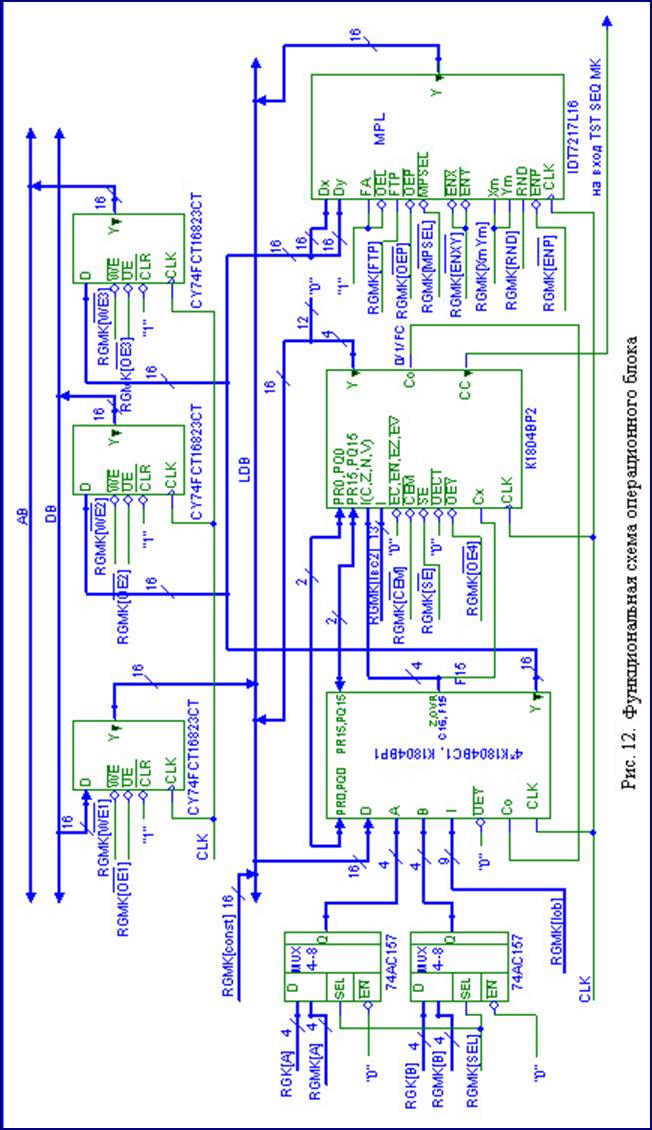

5.3 Функциональная схема ОБ

Теперь(как по рекурсии) можно «подниматься» вверх по уровням структурного описания. Функциональная схема ОБ представлена на рис. 12.

Предполагается, что используется память

асинхронного типа, что означает, что память не имеет встроенного RG

адреса и RG данных.

Выбор регистров RGDin, RGDout, RGA был остановлен на регистрах фирмы Texas Instruments CY74FCT16823СT, как на наиболее

быстродействующих по сравнению с отечественными аналогами (время задержки CLK->Y = 5 нс) и

имеющих входы разрешения записи (![]() ) [10]. Параллельный умножитель выбирался так же по скоростным данным, поэтому был выбран

MPL фирмы IDT (IDT7217L16 – самый

быстродействующий из этой серии)

[8]. Мультиплексор был выбран так же из зарубежной элементной базы 74AC157 (SEL-> Y=5.5 нс) аналог

отечественного КР1554КП16(SEL->Y=9

нc) [3].

) [10]. Параллельный умножитель выбирался так же по скоростным данным, поэтому был выбран

MPL фирмы IDT (IDT7217L16 – самый

быстродействующий из этой серии)

[8]. Мультиплексор был выбран так же из зарубежной элементной базы 74AC157 (SEL-> Y=5.5 нс) аналог

отечественного КР1554КП16(SEL->Y=9

нc) [3].

5.4 Краткое описание работы ОБ

С приходом положительного фронта синхроимпульса данные с DB фиксируются в регистре входа RGDin. В зависимости от определённых битов на порт D ЦПЭ подаются данные от 4-х источников с LDB. В зависимости от управляющей инструкции над данными производится какая-либо операция. После выполнения, с шины Y данные поступают одновременно в регистр адреса памяти (РАП), в выходной регистр данных (RGDout) и MPL, в зависимости, от микрокоманды данные предназначаются для одного из приёмников. В зависимости от результата операции формируются четыре флага и через схему управления сдвигами и состоянием К1804ВР2 передается на вход условия МУУ. Адреса РОН могут браться как из регистра команд (RGK), так и регистра микрокоманд (RGMK), выбор осуществляется из RGMK путем подачи управляющего бита на мультиплексоры MUXA и MUXB.

RGDout должен фиксировать данные в конце текущего цикла и сохранить их в течении последующего цикла обращения к памяти по записи.

Т.к. источником данных и адресов является ЦПЭ на пересылку их в RGDout и RGA необходимо израсходовать 2-а цикла (1- RGA, 2-RGDout). Во избежании порчи содержимого RGA во 2-м цикле необходимо запретить запись в него.

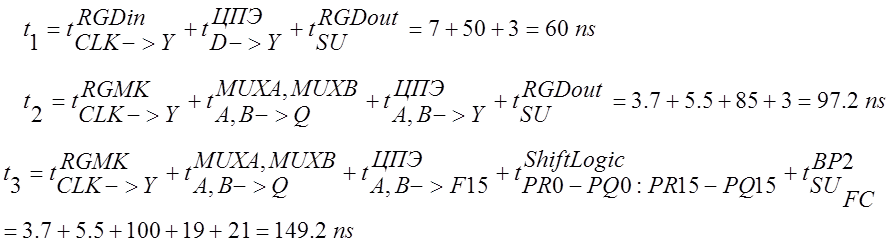

5.5 Расчет минимально допустимой длительности цикла ОБ

При оценке длительности цикла, отыскивается так называемый критический путь распространения сигнала (тракт), который вносит минимальную задержку. Для нахождения такого тракта рассматриваются наиболее длинные тракты, последоваSтельно оценивая для каждого из них задержки, вносимые отдельными элементами.

Из данного анализа видно, что максимальная задержка составляет 149.2нс. Следовательно, минимальная длительность синхросигнала не должна быть меньше этой величины.

6. Разработка детализированной структуры микропрограммного устройства управления

6.1Конвейеризация [5,7]

Конвейеризация возможна, если некоторый процесс обработки информации можно разбить на ряд фаз или этапов и осуществима, если каждый этап обработки реализуется индивидуальным устройством.

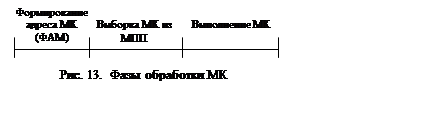

Обработка МК в микропрограммных устройствах включает три фазы (рис.13).

Порядок

выполнения фаз определяется структурой МУУ.

Порядок

выполнения фаз определяется структурой МУУ.

Наименьшей производительностью обладают последовательные МУУ, обработка МК в которых складывается из трёх перечисленных последовательно выполняемых этапов. Использование принципа конвейерной обработки увеличивает максимальную тактовую частоту, т.е. увеличивается производительность за счёт совмещения операций во времени выполняющихся разными функциональными устройствами.

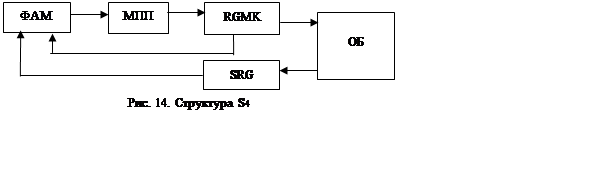

Разрабатываемое МУУ выполнено по двухуровневой

конвейерной структуре, признаком которой является наличие одного конвейерного

регистра RGMK. В работе [4] (стр. 87-91) данная структура

имеет идентификатор S4.

Разрабатываемое МУУ выполнено по двухуровневой

конвейерной структуре, признаком которой является наличие одного конвейерного

регистра RGMK. В работе [4] (стр. 87-91) данная структура

имеет идентификатор S4.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.