Министерство образования и науки РФ

Федеральное агентство по образованию

Новосибирский государственный технический университет

|

Кафедра вычислительной техники

Курсовая работа

По дисциплине «Моделирование»

Факультет: АВТ

Группа: АМ - 610

Студенты: Баласов Д. И.

Преподаватель: Шалагинов А. В.

Новосибирск,

2009

Оглавление

1. Постановка задачи: 3

2. Индивидуальное задание: 3

3. Условно-графическое обозначение (УГО) моделируемого узла. 3

4. Таблица назначения выводов. 4

5. Логические таблицы режимов работы.. 4

6. Таблица реальных задержек. 5

7. Описание работы проектируемого узла. 6

8. OrCAD 9.1. SPICE – проект. 6

8.1. Условно-графическое обозначение проектируемого узла в виде иерархического символа. 6

8.2. Схема замещения проектируемого узла (SPICE – проект). 7

8.3. Схема верификации иерархического символа. 8

8.4. Оценка предельных скоростных (частотных) возможностей исследуемого узла. 13

9. OrCAD 9.1. PCB Simulate – проект. 14

9.1. Схема верификации проектируемого узла. 14

9.2. Схема замещения проектируемого узла (PCB Simulate – проект). 15

9.3. Результаты моделирования схемы приведенной на рис.10. 16

9.4. Сравнение результатов моделирования SPICE и PCD Simulate проектов. 19

10. Поведенческая VHDL-модель узла. 19

11. Схема верификации символа с подключенной к нему VHDL-моделью. 20

12. Active – HDL 8.1. 25

12.1. Условно-графическое обозначение проектируемого узла. 25

12.2. Схема замещения проектируемого узла (Active – HDL 8.1). 26

13. Поведенческая модель на языке VHDL. 27

14. Схема верификации. 28

15. Результаты моделирования. 29

Выводы и личные впечатления. 31

Список литературы. 33

1. Постановка задачи: Разработать цифровой узел, создать его структурные и поведенческие модели на языке VHDL в пакетах OrCAD 9.1 и Active-HDL 8.1. Провести имитационные эксперименты с разработанным узлом, целью которых является подтверждение работоспособности узла и проверка на соответствие его временных задержек требуемым.

2. Индивидуальное задание:

Разработать четырёхразрядный синхронный двоичный реверсивный счётчик с параллельной загрузкой (в качестве прототипа можно выбрать цифровую ИМС типа КР1533ИЕ13), построить для него структурные и поведенческие модели в САПР OrCAD 9.1 и Active-HDL 8.1.

Компьютерным моделированием в названных выше пакетах подтвердить правильность функционирования разработанного узла (функциональное моделирование) и соответствие его временных параметров требуемым (временное моделирование).

Временные задержки и требования к временным соотношениям сигналов на входах должны соответствовать имеющемуся прототипу.

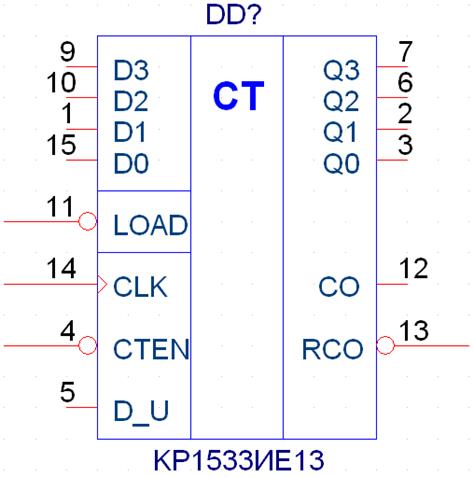

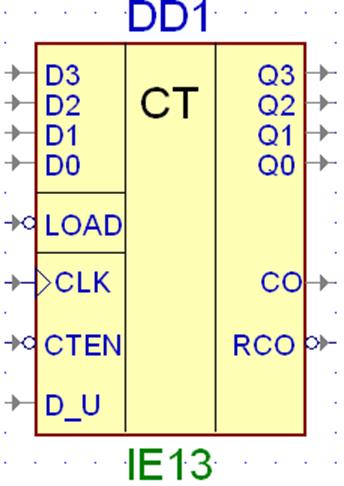

3. Условно-графическое обозначение (УГО) моделируемого узла

Микросхема KP1533ИЕ13 представляет собой четырёхразрядный синхронный двоичный реверсивный счётчик с параллельной загрузкой (аналог зарубежной микросхемы 74ALS191A) [1].

УГО микросхемы, выполненные в различных САПР, приведены на рисунках 1.1 и 1.2.

Рис.1.1 УГО разрабатываемого счётчика, Рис.1.2 УГО разрабатываемого счётчика,

выполненное в пакете OrCAD 9.1 выполненное в пакете Active-HDL 8.1

4. Таблица назначения выводов

|

№ |

Наименование |

Назначение |

|

|

9 |

D3 |

Информационные входы параллельной загрузки (D3 – старший разряд) |

|

|

10 |

D2 |

||

|

1 |

D1 |

||

|

15 |

D0 |

||

|

11 |

LOAD |

Вход стробирования предварительной записи. При подаче на данный вход сигнала низкого уровня на выходы элемента будут передаваться сигналы с информационных входов. |

|

|

14 |

CLK |

Тактовый (счетный) вход |

|

|

4 |

CTEN |

Вход разрешения счета. Счет происходит во время подачи на данный вход сигнала высокого уровня по переднему фронту CLK. |

|

|

5 |

D_U |

Вход выбора направления счета. При низком уровне сигнала счет в прямом направлении, при высоком уровне сигнала - в обратном направлении. |

|

|

7 |

Q3 |

Выходы разрядов счетчика (Q3 – старший разряд) |

|

|

6 |

Q2 |

||

|

2 |

Q1 |

||

|

3 |

Q0 |

||

|

12 |

CO |

Выход переноса. Устанавливается в состояние лог. "1" при высоком уровне сигнала на всех выходах разрядов счетчика в режиме прямого счета, либо при низком уровне сигнала на всех выходах разрядов счетчика в режиме обратного счета. |

|

|

13 |

RCO |

Вход наращивания счета. Предназначен для каскадирования счетчиков. Устанавливается в состояние лог. "0" при наличии сигнала СО в обратной фазе сигнала CLK. |

Таблица 1. Назначения выводов разрабатываемого счётчика с пояснениями функций.

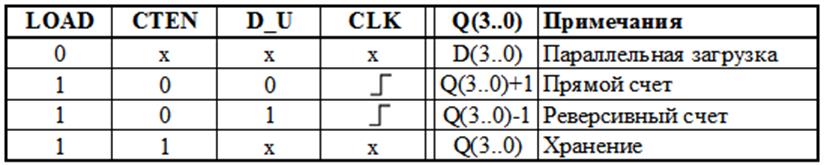

5. Логические таблицы режимов работы

Таблица 2.1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.