Министерство образования и науки Российской Федерации

Федеральное агентство по образованию

Государственное образовательное учреждение

высшего профессионального образования

Новосибирский государственный технический университет

Кафедра вычислительной техники

Курсовая работа

по дисциплине «Моделирование»

Факультет: АВТ

Группа: АМ-411

Студент: Храмцов А.О.

Дата сдачи:

Преподаватель: Шалагинов А. В.

Новосибирск, 2007

Содержание

1. Постановка задачи. 3

2. УГО моделируемого узла. 3

3. Таблица назначения выводов. 3

4. Логическая таблица режимов работы. 4

5. Таблица реальных задержек. 4

6. Описание работы проектируемого узла. 5

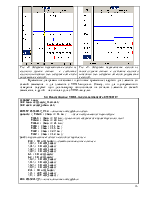

7. Проектирование микросхемы КП17 в пакете DesignLab 8. 5

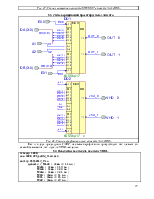

7.1. УГО проектируемого узла. 5

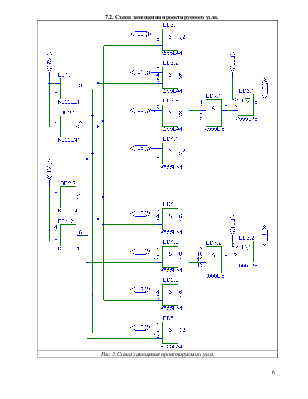

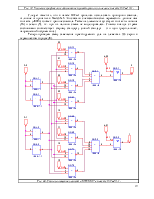

7.2. Схема замещения проектируемого узла. 6

7.3. Текстовое SPICE-описание моделируемого узла. 7

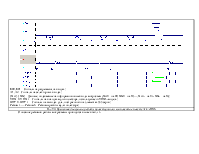

7.4. Содержимое файла описания внешних воздействий. 8

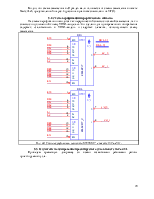

7.5. Схема верификации иерархического символа. 9

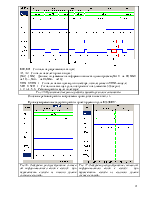

7.6. Результаты моделирования узла. 9

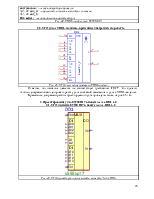

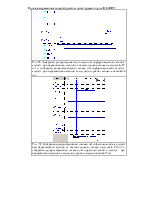

7.7. Оценка предельных скоростных возможностей элемента К555КП17. 12

7.8. Функциональное описание узла с помощью примитивов. 16

7.9. Схема верификации символа с подключенной к нему макромоделью. 18

7.10. Интересные моменты работы К555КП17. 18

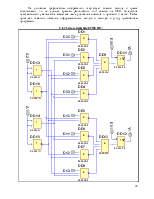

8. Проектирование мультиплексора К555КП17 в пакете OrCad 9.1. 18

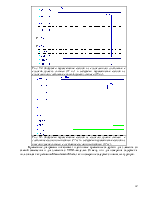

8.1. Иерархический символ и его схема замещения. 18

8.2. Схема верификации иерархического символа. 20

8.3. Результаты моделирования проектируемого узла в пакете OrCad 9.1. 20

8.4. Поведенческая VHDL-модель компонента К555КП17. 23

8.5. УГО узла с VHDL-моделью, временные диаграммы его работы. 25

9. Проектирование узла К555КП17 в пакете Active-HDL 6.2. 25

9.1. УГО элемента К555КП17 в пакете Active-HDL 6.2. 25

9.2. Схема замещения К555КП17. 26

9.3. Схема верификации проектируемого элемента. 27

9.4. Поведенческая модель на языке VHDL. 27

9.5. Временные диаграммы работы проектируемого узла. 29

Выводы и личные впечатления. 33

Список литературы. 36

Приложения ………………………………………………………………………………………..…37

Разработать цифровой узел, создать его структурные и поведенческие модели в пакетах DesignLab 8, OrCAD 9.1, ActiveHDL 6.2. Провести имитационные эксперименты с разработанным узлом, целью которых является подтверждение работоспособности узла и проверка на соответствие его временных задержек требуемым. Также в выводах по работе необходимо привести сравнительный анализ использованных инструментальных средств проектирования и личные впечатления о них.

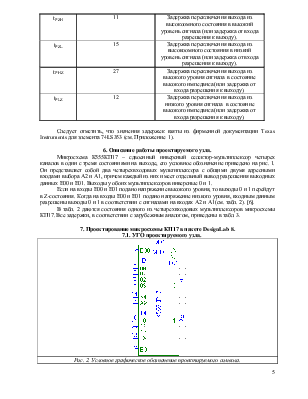

Разрабатываемый узел – КП17 (сдвоенный инверсный селектор-мультиплексор четырех каналов в один с тремя состояниями на выходе). Он представляет собой два четырехвходовых мультиплексора с общими двумя адресными входами выбора, причем каждый из мультиплексоров имеет отдельный вывод разрешения выходных данных. В качестве элементной базы взята серия К555. Зарубежный аналог исследуемого устройства – 74LS353.

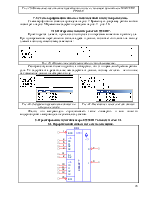

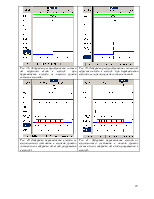

Условное графическое обозначение моделируемого узла взято из книги [1] или [4].

|

|

|

|

|

Рис.1. Условное графическое обозначение моделируемого компонента в пакетах DesignLab 8, OrCAD 9.1 и Active HDL 6.1 соответственно. |

||

Пояснения по поводу различия условных графических изображений приводятся ниже по тексту.

Таблица 1. Выводы компонента К555КП17 и их назначение.

|

Номер вывода |

Название |

Назначение вывода |

|

Входы |

||

|

1,15 |

Е00, Е01 |

Выводы разрешения выходных данных первого и второго мультиплексора соответственно (при подаче на эти входы напряжения высокого уровня, выходы микросхемы переходят в высокоомное или Z-состояние). |

|

2, 14 |

А2, А1 |

Два адресных входа выбора данных, причем А2 – старший разряд, А1– младший разряд. |

|

3,4,5,6 |

DI 03,02,01,00 |

Группа информационных входов первого мультиплексора. |

|

10,11,12,12 |

DI 13,12,11,10 |

Группа информационных входов второго мультиплексора. |

|

Выходы |

||

|

7, 9 |

0, 1 |

Инверсные выходы первого и второго мультиплексора. Переводятся в Z-состояние высоким уровнем напряжения на входах Е00 и Е01 соответственно. На них передаются сигналы с информационных входов в соответствии с сигналами на входах А2 и А1. |

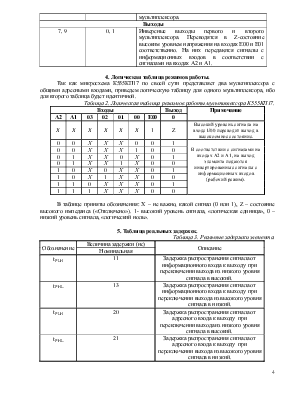

Так как микросхема К555КП17 по своей сути представляет два мультиплексора с общими адресными входами, приведем логическую таблицу для одного мультиплексора, ибо для второго таблица будет идентичной.

Таблица 2. Логическая таблица режимов работы мультиплексора К555КП17.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.