Соединив последовательно несколько триггерных схем – делителей частоты на два, получим простейший многоразрядный двоичный делитель. Более общее название для делителей частоты – счетчики.

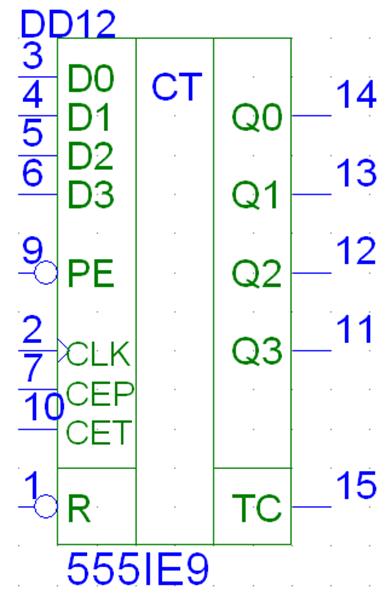

Микросхема К555ИЕ9 – декадный двоично-десятичный счетчик. Он запускается положительным перепадом тактового импульса и имеет синхронную загрузку (предварительную установку каждого триггера). Несколько счетчиков ИЕ9 образуют синхронный многодекадный счетчик. Сброс всех триггеров асинхронный по общему входу сброса R.

Счетчик ИЕ9 – полностью программируемый, на каждом из его выходов можно установить требуемый логический уровень. Напряжение низкого уровня , поступившее на вход параллельной загрузки PE, останавливает счет и разрешает подготовленным на входах D0-D3 данным загрузиться в счетчик в момент прихода следующего перепада тактового импульса (от L к H).

Специально для синхронного каскадирования микросхема имеет два входа разрешения: СЕР (параллельный) и СЕТ (вспомогательный, с условным названием «трюковый»), а также выход ТС (окончание счета).

Счетчик считает тактовые импульсы, если на обоих его входах СЕР и СЕТ напряжение высокого уровня. Вход СЕТ последующего счетчика получает разрешение счета в виде напряжения высокого уровня от выхода ТС предыдущего счетчика.

Для счетчиков ИЕ9 не допускаются перепады от высокого уровня к низкому на входах СЕР и СЕТ, если на тактовом входе присутствует напряжение низкого уровня. Нельзя подавать положительный перепад на вход РЕ, если на тактовом входе присутствует напряжение низкого уровня, а на входах СЕТ и СЕР – высокого ( во время перепада или перед ним). Сигналы на входах СЕР и СЕТ можно изменять, если на тактовом входе С присутствует напряжение низкого уровня. Когда на входе РЕ появляется высокий уровень, а входы СЕ не активны (т.е. не используем СЕТ и СЕР и на них остается низкий уровень), то вместе с последующим положительным перепадом тактового импульса на выходах Q0-Q3 появится код от входов D0-D3.

Запуская напряжениями высокого уровня входы СЕТ и СЕР во время низкоуровневой части тактового периода, получим на выходах наложение кодов загрузки и внутреннего счета. Если во время низкоуровневой части периода тактовой последовательности на входы СЕТ, СЕР и РЕ поданы положительные перепады, нарастающие от низкого уровня к высокому, тактовый перепад изменит код на выходах Q0-Q3 на последующий.

Рис. 4. УГО микросхемы К555ИЕ9

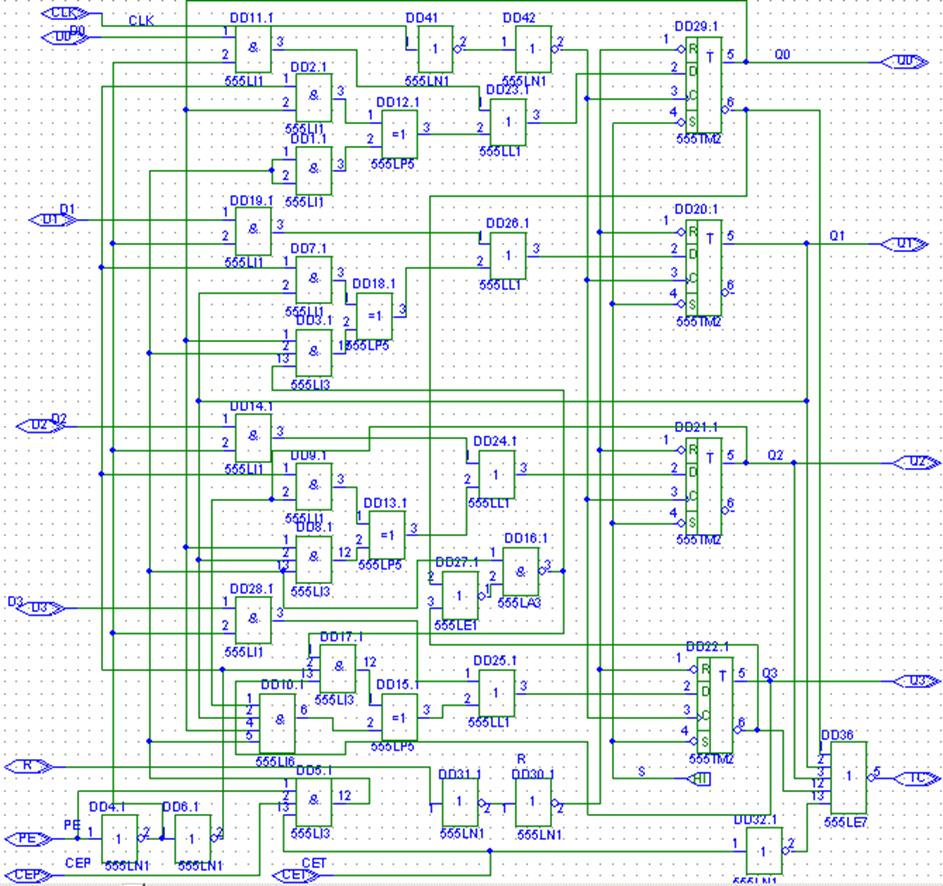

Рис.5. Принципиальная схема микросхемы К555ИЕ9

SHEMA_1.cir

* C:\MSim_8\UserLib\SHEMA_1.sch

* Schematics Version 8.0 - July 1997

* Tue Oct 19 03:07:17 2004

** Analysis setup **

.tran 20ns 4000ns

.STMLIB "C:\MSim_8\UserLib\Shema_555.stl"

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "C:\MSim_8\UserLib\555IE9.LIB"

.lib "nom.lib"

.stmlib "C:\MSim_8\UserLib\111.stl"

.INC "SHEMA_1.net"

.INC "SHEMA_1.als"

.probe

.END

SHEMA_1.net * Schematics Netlist *

U_DSTM7 STIM(4,0) $G_DPWR $G_DGND D3 D2 D1 D0 IO_STM STIMULUS=D

U_DSTM4 STIM(1,0) $G_DPWR $G_DGND CET IO_STM STIMULUS=CET

U_DSTM3 STIM(1,0) $G_DPWR $G_DGND CEP IO_STM STIMULUS=CEP

U_DSTM2 STIM(1,0) $G_DPWR $G_DGND PE IO_STM STIMULUS=PE

U_DSTM1 STIM(1,0) $G_DPWR $G_DGND R IO_STM STIMULUS=R

U_DSTM5 STIM(1,0) $G_DPWR $G_DGND C IO_STM STIMULUS=C

X_DD9_DD2_1 $N_0001 $N_0001 $N_0002 $G_DPWR $G_DGND 555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD9_DD4_1 Q0 $N_0001 $N_0004 $N_0003 $G_DPWR $G_DGND 555LI3 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD9_DD9_1 $N_0001 $N_0005 $N_0004 $G_DPWR $G_DGND 555LA3 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD9_DD11_1 $N_0006 $N_0003 $N_0007 $G_DPWR $G_DGND 555LP5 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.