МИНИСТЕРСТВО ВЫСШЕГО И ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

НОВОСИБИРСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

Кафедра вычислительной техники

Расчётно-графическая работа

по схемотехнике

“Разработка модуля памяти”

Факультет: АВТ

Группа: АМ-209

Студент: Майснер М.Ю.

Преподаватель: Соболев В.И.

Новосибирск

2004

Содержание

Данная расчетно-графическая работа выполнена по курсу «Схемотехника» пройденного за 5-ый семестр с надеждой на приобретение первого опыта проектирования цифровых устройств. Объектом разработки является модуль асинхронный памяти, разрабатывая который…

1.Цели разработки и исходные данные.

1.1 Цели разработки:

Задача данной расчетно-графической работы заключается в разработке модуля асинхронной памяти основные требования которого определяются техническим заданием. Он должен обеспечивать:

· высокое быстродействие;

· простоту и надежность схемных решений.

Необходимо также обеспечить отсутствие в схемах критических временных соотношений, риска сбоя и гонок сигналов.

1.2 Исходные данные:

Тип памяти: SRAM

Информационная организация: 64К×36 (с контролем паритета)

Максимальное время цикла: 80нс

2.Разработка структуры модуля памяти.

2.1 Общее структурное описание:

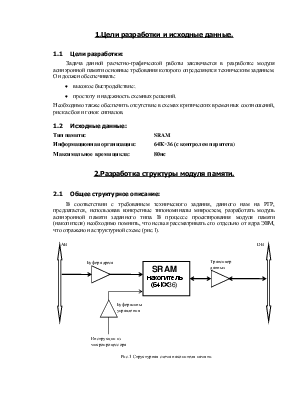

В соответствии с требованием технического задания, данного нам на РГР, предлагается, использовав конкретные типономиналы микросхем, разработать модуль асинхронной памяти заданного типа. В процессе проектирования модуля памяти (накопителя) необходимо помнить, что нельзя рассматривать его отдельно от ядра ЭВМ, что отражено на структурной схеме (рис.1).

Рис.1 Структурная схема накопителя памяти.

На структурной схеме изображены следующие элементы: шины адреса (AB) и данных (DB) посредством которых происходит взаимодействие с элементами системы микропроцессора; SRAM накопитель, состоящий из нескольких микросхем, обеспечивающих заданную информационную организацию; буферы адреса и шины управления, снижающие нагрузку на шины адреса и управления соответственно; трансивер данных (двунаправленный буфер), также снижающий нагрузку на шину данных.

2.2 Выбор конкретного типономинала ИМС:

Микросхемы памяти выбирались исходя из следующих критериев:

· требуемая информационная емкость

· требуемое время цикла

· совместимость электрического интерфейса (соответствие стандарту ТТЛ)

также учитывалось, чтобы при построении модуля памяти их количество было наименьшим (для уменьшения затрат на сопряжение микросхем).

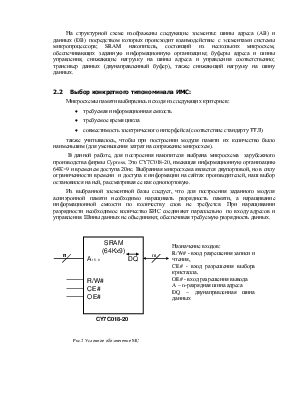

В данной работе, для построения накопителя выбрана микросхема зарубежного производства фирмы Cypress. Это CY7C018-20, имеющая информационную организацию 64К×9 и временем доступа 20нс. Выбранная микросхема является двупортовой, но в силу ограниченности времени и доступа к информации на сайтах производителей, наш выбор остановился на ней, рассматривая ее как однопортовую.

Из выбранной элементной базы следует, что для построения заданного модуля асинхронной памяти необходимо наращивать разрядность памяти, а наращивание информационной емкости по количеству слов не требуется. При наращивании разрядности необходимое количество БИС соединяют параллельно по входу адресов и управления. Шины данных не объединяют, обеспечивая требуемую разрядность данных.

Рис.2 Условное обозначение МС

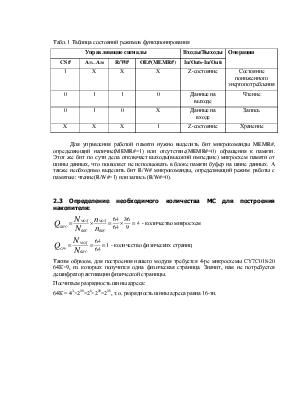

Табл.1 Таблица состояний режимов функционирования

|

Управляющие сигналы |

Входы/Выходы |

Операция |

|||

|

CS# |

A31…A30 |

R/W# |

OE#(MEMR#) |

In/Out0-In/Out8 |

|

|

1 |

X |

X |

X |

Z-состояние |

Состояние пониженного энергопотребления |

|

0 |

1 |

1 |

0 |

Данные на выходе |

Чтение |

|

0 |

1 |

0 |

X |

Данные на входе |

Запись |

|

X |

X |

X |

1 |

Z-состояние |

Хранение |

Для управления работой памяти нужно выделить бит микрокоманды MEMR#, определяющий наличие(MEMR#=1) или отсутствие(MEMR#=0) обращения к памяти. Этот же бит по сути дела отключает выходы(высокий импеданс) микросхем памяти от шины данных, что позволяет не использовать в блоке памяти буфер на шине данных. А также необходимо выделить бит R/W# микрокоманды, определяющий режим работы с памятью: чтение(R/W#=1) или запись (R/W#=0).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.