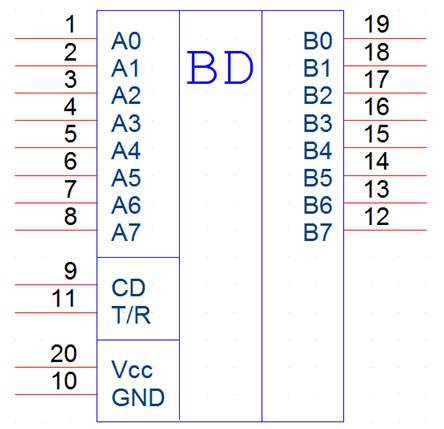

Рис. 5. УГО Intel 8286

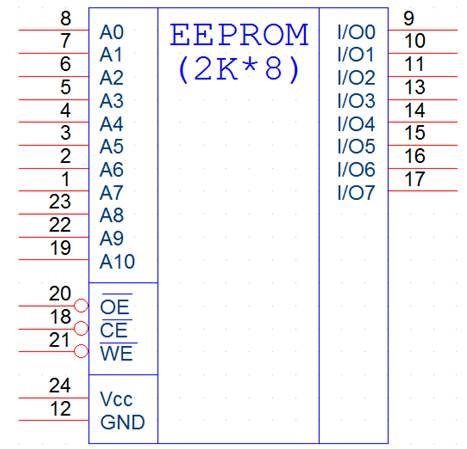

Высокопроизводительное EEPROM c низким энергопотреблением. Изготавливается по КМОП технологии, входы и выходы КМОП и ТТЛ совместимы. Память содержит 16 килобит, организованных в 2К слов по 8 бит.

Таблица 6. Выводы БИС AT28C16

|

№ |

Обозначение |

Тип |

Функциональное назначение |

|

8-1, 23, 22,19 |

A0-A10 |

Вход |

Адрес |

|

18 |

~CE |

Вход |

Разрешение работы чипа: низкий уровень разрешает работу памяти |

|

20 |

~OE |

Вход |

Разрешение вывода: низкий уровень сигнала разрешает вывод данных на шину. |

Окончание таблицы 2.

|

№ |

Обозначение |

Тип |

Функциональное назначение |

|

21 |

~WE |

Вход |

Разрешение записи: низкий уровень сигнала разрешает запись данных в память |

|

9-11, 13-17 |

I/O0-I/7 |

Выход\Выход |

Входы/Выходы данных |

|

24, 12 |

Vcc, GND |

Питание и земля. |

Рис. 6. УГО AT28C16

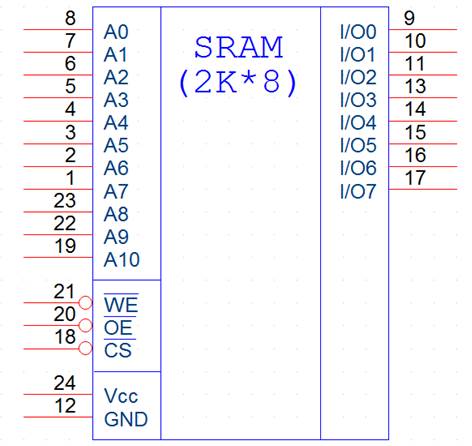

Высокопроизводительное SRAM c низким энергопотреблением. Изготавливается по КМОП технологии, входы и выходы КМОП и ТТЛ совместимы. Память содержит 16 килобит, организованных в 2К слов по 8 бит.

Таблица 7. Выводы БИС ITD6116SA

|

№ |

Обозначение |

Тип |

Функциональное назначение |

|

8-1, 23, 22,19 |

A0-A10 |

Вход |

Адрес |

|

18 |

~CE |

Вход |

Разрешение работы чипа: низкий уровень разрешает работу памяти |

|

20 |

~OE |

Вход |

Разрешение вывода: низкий уровень сигнала разрешает вывод данных на шину. |

|

21 |

~WE |

Вход |

Разрешение записи: низкий уровень сигнала разрешает запись данных в память |

|

9-11, 13-17 |

I/O0-I/7 |

Выход\Выход |

Входы/Выходы данных |

|

24, 12 |

Vcc, GND |

Питание и земля. |

Рис. 7. УГО ITD6116SA

Строить микропроцессорную систему будем на микропроцессоре I-8085A, хотя можно было использовать его отечественный аналог KР1821BM85. Данный процессор является усовершенствованным процессором I-8080. Развитие технологий позволило внести на кристалл БИС, которых не было на кристалле процессора I-8080, а именно ГТИ, контроллер прерываний, системный контроллер, а также УАПП. Таким образом, нам не придется использовать отдельные чипы ГТИ и системного контроллера. Для экономии ножек процессор использует мультиплексированную шину адреса\данных, причем шина данных имеет ширину 8 бит, а шина адреса 16 бит, поэтому мультиплексируется, только младшая часть шины адреса. Процессор позволяет адресовать 256 устройств ввода-вывода, при этом адрес устройства дублируется на старшую и младшую часть шины адреса, режим работы устройства (чтение, запись) управляется соответствующими сигналами микропроцессора.

Поскольку шина данных и младшая часть шины адреса мультиплексированные нам понадобится буферный регистр, в который будет записываться младшая часть адреса по сигналу процессора. В качестве регистра выбран регистр Intel 8282.

К шинам данных и адреса подключается большое количество устройств, поэтому, чтобы обеспечить необходимый ток шины придется буферизовать. Шина данных является двунаправленной, поэтому вместо буфера будем использовать шинный формирователь, используем шинный формирователь и для буферизации старшей части шины адреса.

В качестве ПЗУ с объёмом 2Кх8 выбрана микросхема памяти AT28C16. Это EEPROM, по заданию требуется ПЗУ, чтобы запретить памяти запись подключим вход ~WR к логической единице.

В качестве ОЗУ с объёмом 2Кх8 выбрана микросхема памяти ITD6116SA с организацией 2Кх8.

В качестве контроллера параллельного интерфейса используется БИС I-8255А.БИС соединяется с внутренними шинами разрабатываемой системы и некоторым гипотетическим устройством по стандарту RS-232 с другой стороны

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.