D8279 EQU 80H ; Порт данных устройства I-8279(КР580ВВ79)

RFIFO EQU 50H ; Команда считывания из ОЗУ типа FIFO c автоинкрементной адресацией

INTEND EQU 0E0H ; Команда сброса запроса на прерывание

ORG 2CH ; Начало области рестарта для прерывания по входу RST 5.5

BEGIN: PUSH PSW ; Сохранение содержимого регистра

PUSH H ;

PUSH B ;

MVI A,RFIFO ; Загрузка в регистр A команды считывания из ОЗУ типа FIFO

OUT C8279 ; Вывод через порт команд I-8279(КР580ВВ79)

LXI H,MATRIX ; Загрузка в HL начального адреса матрицы

MVI B,8 ; Загрузка счетчика (регистр B)

LOOP: IN D8279 ; Ввод сенсорной матрицы

MOV M,A ; Сохранение в памяти

INX H ; Увеличение значения указателя

DCR B ; Уменьшение значения счетчика

JNZ LOOP ; Переход, если значение счетчика не 0

POP B ; Восстановление содержимого регистров

POP H ;

POP PSW ;

EI ; Разрешение прерываний

RET ; Возврат в основную программу

ORG 2000H ; Определение начального адреса матрицы

MATRIX: DS 8 ; 8 байт памяти

END BEGIN

На рисунке 3.1 представлена упрошенная блок-схема микропроцессора К1821ВМ85. Аккумулятор соединен с шиной данных и арифметико-логическим устройством (АЛУ). АЛУ выполняет все преобразования данных, как, например, увеличение числа на 1 или сложение двух чисел.

Временный регистр обеспечивает другой вход АЛУ. Этот регистр недоступен программисту и управляется автоматически схемой управления микропроцессора.

Флаговый регистр представляет собой набор триггеров, которые указывают определенные характеристики результата самой последней операции, выполненной АЛУ. Например, признак нуля устанавливается, если результатом операции является нуль. Признак нуля проверяется командой JZ.

Регистр команд, дешифратор команд, счетчик команд и логические схемы управления и синхронизации используются для выборки команд из памяти и управления их выполнения.

Предположим, например, что команда, которую нужно выполнить, находится в ячейке с адресом 0200. Прежде всего необходимо прочитать из памяти код операции, т.е. произвести выборку команды. Счетчик команд (СК), который содержит требуемый адрес 0200, воздействует на адресную шину, в результате чего выбирается ячейка памяти с адресом 0200. ПЗУ выдает содержимое ячейки 0200 (предположительно код операции) на шину данных, и микропроцессор запоминает код операции в регистре команд.

Информация из регистра команд поступает на дешифратор команд (ДК), который распознает код операции и выдает сигнал управления на устройство управления и синхронизации. Устройство управления и синхронизации напоминает собой процессор внутри процессора. Имеющееся в интегральной схеме микропроцессора ПЗУ содержит микрокод или микрокоманду, которая точно указывает процессору, что надлежит делать, чтобы выполнить каждую команду на машинном языке. Система микрокоманд, которая является частью конструкции микропроцессора и обычно не может быть изменена, определяет машинный язык микропроцессора.

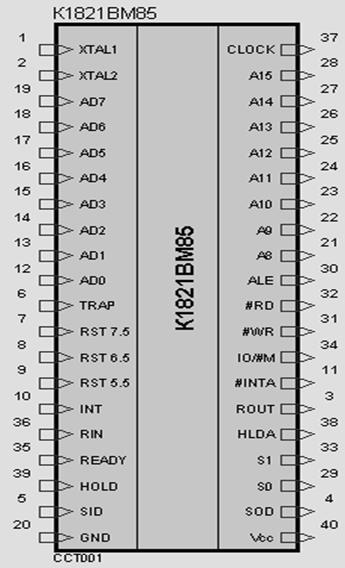

Условное графическое обозначение (УГО) К1821ВМ85 приведено на рисунке 3.2. Назначение каждого вывода описывается в таблице 3.1.

|

Рисунок 3.1 - Упрощенная блок-схема микропроцессора К1821ВМ85

Рисунок 3.2 - УГО К1821ВМ85

Микропроцессор К1821ВМ85 может выполнять операции четырех основных типов (1, с. 72):

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.