Основные достоинства ШФ: большой выходной ток при малом входном токе и отсутствие шума на выходе при переключениях.

Назначение каждого вывода описывается в таблице 3.7.

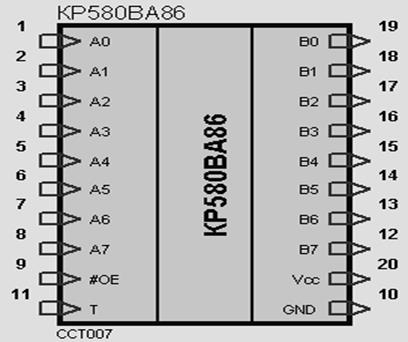

УГО КP580BA86 приведено на рисунке 3.12.

Таблица 3.7 – Выводы восьмиразрядного шинного формирователя КР580ВА86

|

Обозначение вывода |

Назначение |

|

A7..A0 |

Вход/выход линий данных. В зависимости от состояния входа Т они могут быть входными, если на Т – сигнал высокого уровня, и выходными, если на Т – сигнал низкого уровня. |

|

B7..B0 |

Вход/выход линий данных. Они является входными, если на Т – сигнал низкого уровня, и выходными, если на Т – сигнал высокого уровня. |

|

Т |

Входной сигнал управления направлением передачи. При Т=0 осуществляется передача от В к А , при Т=1 – от А к В. Сигнал Т выбирает верхний или нижний усилитель-формирователь, разрешая соответствующую передачу. |

|

#OE |

Входной сигнал разрешения передачи. При #OE=0 снимается z-состояние с выхода усилителя-формирователя, выбранного по входу Т. Переход в z-состояние наоборот не дает отрицательных выбросов на выводах ИС. |

Рисунок 3.12 - УГО KР580ВА86

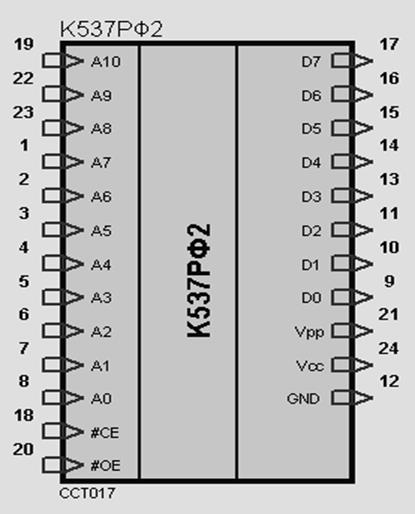

К537РФ2 –ПЗУ с ультрафиолетовым стиранием информации, имеет емкость 2 килобайта и допускает 100 циклов программирования. Напряжение перепрограммирования 25 В. Считывание информации из микросхемы происходит в асинхронном режиме доступа к накопителю.

Режимы программирования микросхемы К537РФ2 приведены в таблице 3.8.

УГО К537РФ2 приведено на рисунке 3.13.

Таблица 3.8 – Режимы программирования К537РФ2

|

Сигнал |

Запись |

Считывание |

Хранение |

|

#CS |

1 |

0 |

1 |

|

#OE |

1 |

0 |

X |

|

Vpp |

25 |

5 |

5 |

Рисунок 3.13 - УГО K537РФ2

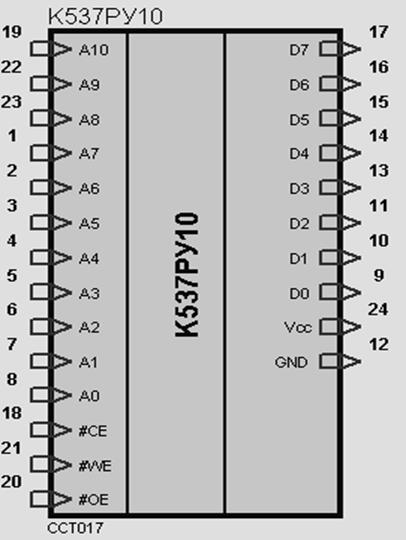

К537РУ10 – статическое оперативно - запоминающее устройство емкостью 2Кх8. Микросхема имеет 8 разрядов шины данных и 11 разрядов шины адреса, позволяющих в произвольном доступе адресоваться к 2К байтам памяти.

Входные сигналы управления определяют работу микросхемы в режиме записи и считывания. При установленном адресе и сигналах #CS=#WE=0, #OE=1 производится запись в ОЗУ установленного на шине данных записываемого байта данных. При установленном адресе и сигналах #CS=#OE=0, #WE=1 производится чтение из памяти выбранного байта на шину данных.

УГО К537РУ10 приведено на рисунке 3.14.

Рисунок 3.14 - УГО K537РУ10

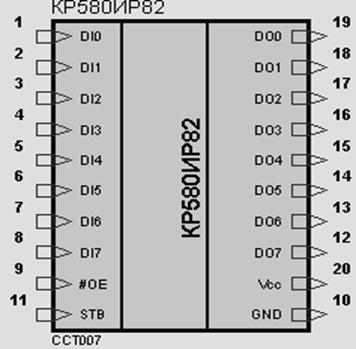

Используются для организации запоминающих буферов, адресных защелок, портов ввода-вывода, мультиплексоров и т.п. Буферные регистры состоят из восьми информационных триггеров с выходными схемами с тремя состояниями, общими сигналами записи информации STB и управления выходными схемами #OE.

При сигнале высокого уровня на входе STB состояние входных линий DI7..DI0 передается на выходные линии DO7..DO0.

Назначение каждого вывода описывается в таблице 3.9.

УГО КP580BA86 приведено на рисунке 3.15.

Таблица 3.9 – Выводы восьмиразрядного шинного формирователя КР580ИР82

|

Обозначение вывода |

Назначение |

|

DI7..DI0 |

Линия входных данных |

|

DO7..DO0 |

Линия выходных данных. |

|

STB |

Стробирующий сигнал. |

|

#OE |

Разрешение выдачи данных. |

Рисунок 3.15 - УГО KР580ИР82

Разработана микропроцессорная система на базе микропроцессора I-8085 (К1821ВМ85), имеющая 2к байта ПЗУ и 2к байта ОЗУ, а также периферийные БИС - программируемое устройство ввода — вывода параллельной информации различного формата I-8255 (КР580ВВ55) и программируемый интерфейс клавиатуры и дисплея I-8279 (КР580ВВ79).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.