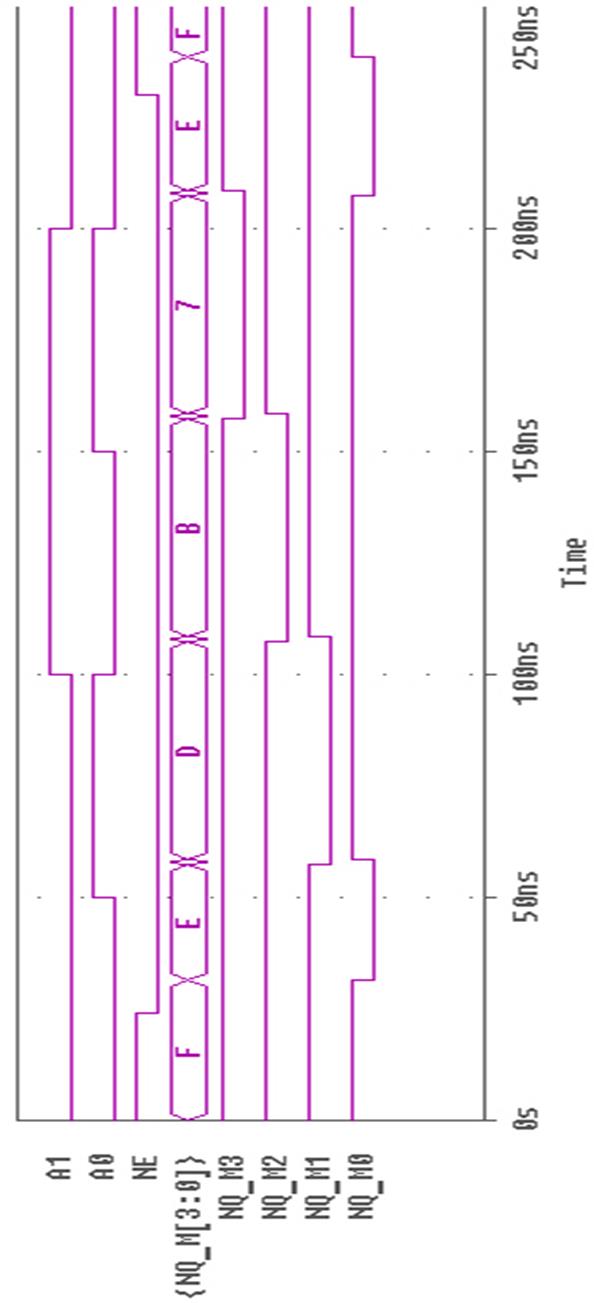

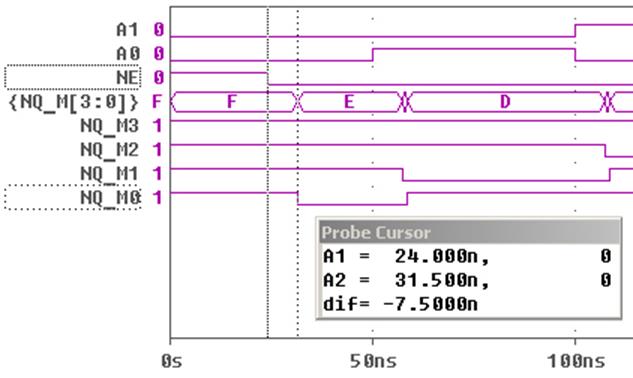

Рис. 19. Пример № 1.

В данном примере показана задержка между включением

дешифратора и выводом данных, т.е. время ![]() и оно

соответствует минимальному значению задержки реального дешифратора и значению с

рис. 8.

и оно

соответствует минимальному значению задержки реального дешифратора и значению с

рис. 8.

Дальнейшее рассмотрение задержек не имеет смысла, так как они идентичны. Кроме того, преподаватель всегда может промоделировать схему приложенную к КР на дискетке и сравнить результаты (файл Test_MacroModel.shm).

Собственно, говоря, задачи поставленные преподавателем по разработке элемента, в данном случае дешифратора ххххИД14, в данном пакете были, надеюсь, благополучно выполнены.

3. Проектирование элемента в OrCad 9.1 [4]

3.1. Иерархический символ (УГО, схема замещения)

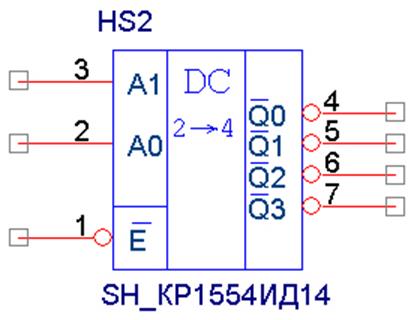

Рис. 20. УГО проектируемого иерархического символа

При создании названия символа применялась кириллица, т.е. не эквивалентное название на английском. С одной стороны это полная адаптация под российского схемотехника, с другой требования настройки пакета для отображения кириллицы (OptionsàPrefences). Опять же при написании VHDL-кода название модели берется в «косые» скобки, т.е. \КР1554ИД14\.

УГО данного символа сохранен в библиотеке вместе со своей схемой замещения. Про данную возможность отдельный абзац в гл. 5. Так же в данную библиотеку внесен символ, поддерживаемый VHDL-моделью.

Основой для проектирования схемы замещения стали вентили, использованные в п. 2.2. Опять же созданные модели данных вентилей не соответствуют реальным элементам по динамическим характеристикам. Ниже приведены VHDL-модели для данных вентилей.

Так как в один корпус ИМС входит несколько вентилей, то приходилось тиражировать одно и тоже описание для разных секций ИМС. Такой подход оправдывается, когда в одном корпусе ИМС содержатся элементы с разными функциями.

Несколько слов об элементе К155ЛН1. Как видно из рис.21, сигнал «Е» подается на не совсем обычный инвертор (точнее не совсем обычное изображение), так вот этот элемент не новый с таким УГО, а всего лишь К155ЛН1 с Converted символом.

--=================== Элемент 3И-НЕ =========================

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

entity \К155ЛА4\ is

port ( \IN1_-1\ : IN std_logic;

\IN2_-1\ : IN std_logic;

\IN3_-1\ : IN std_logic;

\OUT_-1\ : OUT std_logic;

GND : IN std_logic;

VCC : IN std_logic;

\IN1_-2\ : IN std_logic;

\IN2_-2\ : IN std_logic;

\IN3_-2\ : IN std_logic;

\OUT_-2\ : OUT std_logic;

\IN1_-3\ : IN std_logic;

\IN2_-3\ : IN std_logic;

\IN3_-3\ : IN std_logic;

\OUT_-3\ : OUT std_logic

);

end;

architecture model of \К155ЛА4\ is

SIGNAL AND_1 : std_logic;

SIGNAL AND_2 : std_logic;

SIGNAL AND_3 : std_logic;

begin

process(\IN1_-1\,\IN2_-1\,\IN3_-1\,\OUT_-1\,AND_1) begin

AND_1<= not (\IN1_-1\and\IN2_-1\and\IN3_-1\);

if (AND_1'EVENT) then--проверка на переключение сигналов

case (AND_1)is

when '1' => \OUT_-1\<=AND_1 after 8.5 ns;--Tplh

when '0' => \OUT_-1\<=AND_1 after 7.5 ns;--Tphl

end case;

end if;

end process;

process(\IN1_-2\,\IN2_-2\,\IN3_-2\,\OUT_-2\,AND_2) begin

AND_2<=not (\IN1_-2\and\IN2_-2\and\IN3_-2\);

if (AND_2'EVENT) then--проверка на переключение сигналов

case (AND_2)is

when '1' => \OUT_-2\<=AND_2 after 8.5 ns;--Tplh

when '0' => \OUT_-2\<=AND_2 after 7.5 ns;--Tphl

end case;

end if;

end process;

process(\IN1_-3\,\IN2_-3\,\IN3_-3\,\OUT_-3\,AND_3) begin

AND_3<=not (\IN1_-3\and\IN2_-3\and\IN3_-3\);

if (AND_3'EVENT) then--проверка на переключение сигналов

case (AND_3)is

when '1' => \OUT_-3\<=AND_3 after 8.5 ns;--Tplh

when '0' => \OUT_-3\<=AND_3 after 7.5 ns;--Tphl

end case;

end if;

end process;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.