1. Разработка дешифратора ххххИД14 (в данной работе за основу «эталонного» дешифратора был взят дешифратор КР1554ИД14), т.е. создания его структурных и поведенческих моделей (на языках SPICE, PML, SimCode, DSL и VHDL в пакетах DesignLab 8, OrCAD 9.1, PCAD 2001).

2. Провести имитационные эксперименты с разработанным узлом, целью которых является подтверждение работоспособности узла и соответствие его временных задержек требуемым.

3. Произвести сравнительный анализ использованных инструментальных средств проектирования.

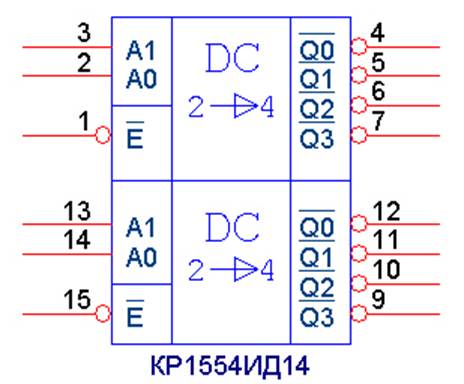

1.2. УГО исследуемого узла

Рис. 1. УГО ИМС КР1554ИД14

1.3. Таблица назначения выводов

|

Номер вывода |

Название вывода |

Назначение вывода |

№ секции |

|

1 |

|

Вход разрешения работы дешифратора 2à4 |

1 |

|

2 |

А0 |

Младший адресный вход |

|

|

3 |

А1 |

Старший адресный вход |

|

|

4 |

|

Выход |

|

|

5 |

|

Выход |

|

|

6 |

|

Выход |

|

|

7 |

|

Выход |

|

|

8 |

GND |

Земля |

|

|

9 |

|

Выход |

2 |

|

10 |

|

Выход |

|

|

11 |

|

Выход |

|

|

12 |

|

Выход |

|

|

13 |

А1 |

Старший адресный вход |

|

|

14 |

А0 |

Младший адресный вход |

|

|

15 |

|

Вход разрешения работы дешифратора 2à4 |

|

|

16 |

Ucc |

Напряжение питания |

|

|

Табл. 1. Назначение выводов ИМС КР1554ИД14 |

|||

1.4. Таблица режимов работы

|

Вход |

Выход |

Примечание |

|||||

|

|

А1 |

А0 |

|

|

|

|

|

|

H |

* |

* |

H |

H |

H |

H |

Дешифратор выключен, все выходы в пассивном состоянии |

|

L |

L |

L |

H |

H |

H |

L |

Перевод выхода |

|

L |

L |

H |

H |

H |

L |

H |

Перевод выхода |

|

L |

H |

L |

H |

L |

H |

H |

Перевод выхода |

|

L |

H |

H |

L |

H |

H |

H |

Перевод выхода |

|

Примечание: L - низкий уровень, H – высокий уровень. Табл. 2. Режимы работы ИМС КР1554ИД14 |

|||||||

Режимы указаны для одной секции, хоть секции и одинаковы, но они не зависимы друг от друга.

1.5. Таблица реальных задержек и параметры временной диаграммы

|

Обозначение |

Параметр |

Min |

Max |

Единица |

|

Время задержки сигнала при включении |

||||

|

|

от

входов An к выходам |

7.5 |

8.5 |

ns |

|

от входа |

||||

|

Время задержки распространения сигнала при выключении |

||||

|

|

от

входов An к выходам |

8.5 |

10 |

ns |

|

от входа |

||||

|

Табл. 3. Динамические характеристики дешифратора КР1554ИД14 |

||||

1.6. Описание работы моделируемого узла

Сдвоенный дешифратор – демультиплексор 2 на 4 с индивидуальным входом выбора и разрешения. Зарубежный аналог 74AC139.

Для того чтобы дешифратор начал выбирать по

поступившим адресам линии необходимо подать сигнал активного уровня на вход ![]() , т.е. фактически разрешить работу. После

данного действия дешифратор выбирает линию по поступившим адресам и переводит

её активное состояние. Для прекращения работы дешифратора, т.е. переход всех

выходов в пассивное состояние, необходимо подать сигнал пассивного уровня на

вход включения.

, т.е. фактически разрешить работу. После

данного действия дешифратор выбирает линию по поступившим адресам и переводит

её активное состояние. Для прекращения работы дешифратора, т.е. переход всех

выходов в пассивное состояние, необходимо подать сигнал пассивного уровня на

вход включения.

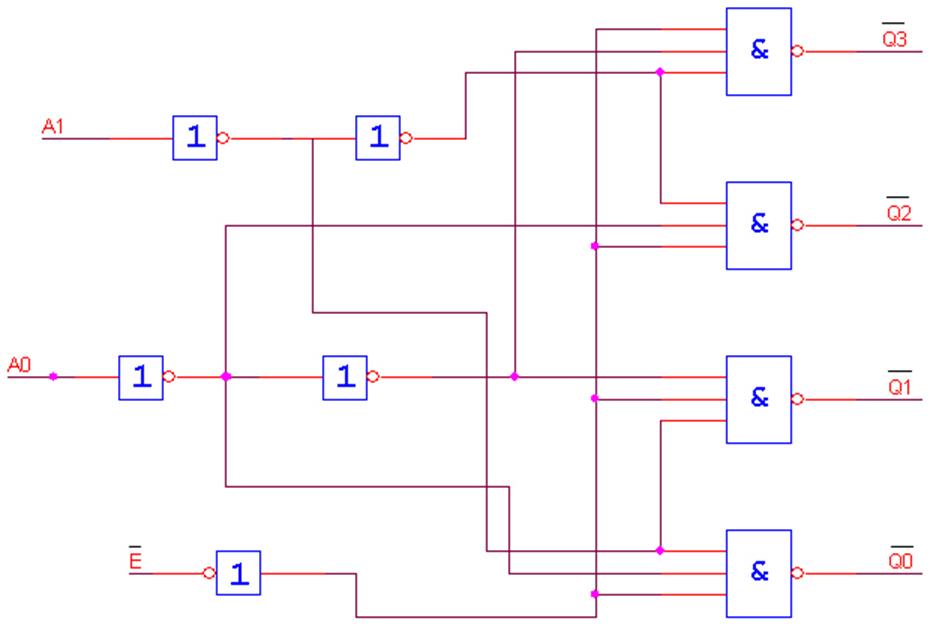

1.7. Функциональная схема исследуемого узла

Рис. 2. Функциональная схема дешифратора КР1554ИД14

Естественно, что данная схема представляет собой схему замещения только одной секции (они идентичны).

2. Проектирование элемента в САПР DesignLab 8.0 [2]

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.