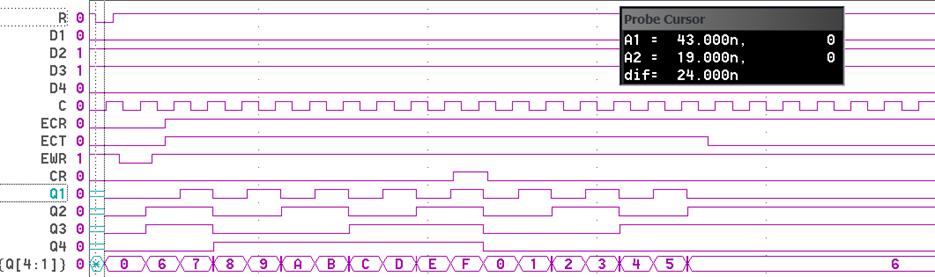

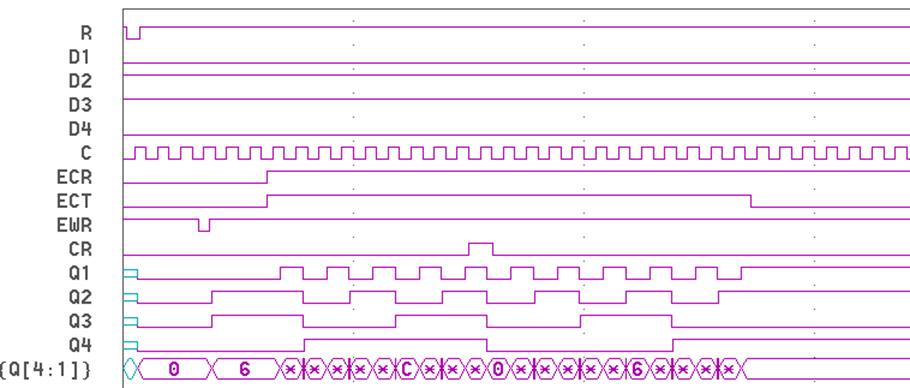

- вход тактирования C – выход данных Q8,Q4,Q2,Q1 – 15нс;

Рис. 9 Задержка распространения сигнала вход cброса

![]() – выход данных Q8,Q4,Q2,Q1 - 24нс;

– выход данных Q8,Q4,Q2,Q1 - 24нс;

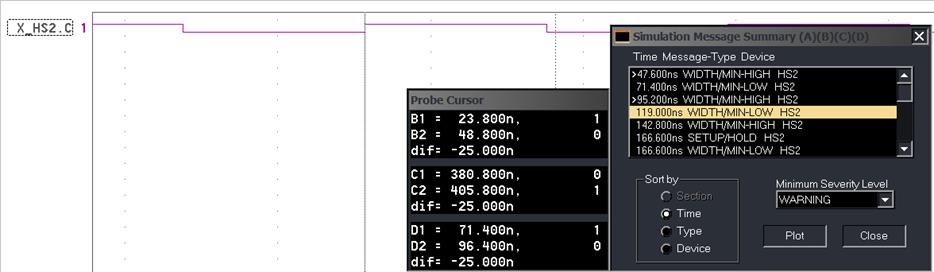

Целью данного пункта курсовой работы является овладение ещё одним мощным инструментом моделирования – высокоуровневым логико-временным моделированием. Теперь мы не собираемся раскрывать структуру объекта, а хотим смоделировать его работу, причём также точно, как если бы он моделировался на низком уровне. Это вовсе не означает, что такой инструмент не предоставляет возможностей по имитации временных соотношений в схеме и нагрузочных характеристик. Всё это можно сделать с помощью прямого функционального описания объекта и его временных характеристик, используя специальные примитивы LOGICEXP, PINDLY и CONSTRAINT.

Ниже приведён вариант реализации такого функционального описания:

**Директива начала макромодели

.SUBCKT 555IE10_macro C_I ECT_I ECR_I NR_I NEWR_I D1_I D2_I D4_I D8_I

+ Q1_O Q2_O Q4_O Q8_O CR_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

**Необходимые объявления

U1 JKFF(4) DPWR DGND $D_HI NR MCLK

+ JA JB JC JD KA KB KC KD

+ Q1 Q2 Q4 Q8 $D_NC $D_NC $D_NC $D_NC

+ D0_EFF IO_STD

*

**Начало примитива LOGICEXP, описывающего логику работы компонента

**Число входов равно 13, а число выходов из лог-го блока – 20.

U161LOG LOGICEXP(13,20) DPWR DGND

+ C_I ECT_I ECR_I NR_I NEWR_I D1_I D2_I D4_I D8_I Q1 Q2 Q4 Q8

+ MCLK CR JA JB JC JD KA KB KC KD C ECT ECR NR NEWR D1 D2 D4 D8 IEN

+ D0_GATE IO_STD IO_LEVEL={IO_LEVEL}

+ LOGIC:

+ C = { C_I }

+ ECT = { ECT_I }

+ ECR = { ECR_I }

+ NR = { NR_I }

+ NEWR = { NEWR_I }

+ D1 = { D1_I }

+ D2 = { D2_I }

+ D4 = { D4_I }

+ D8 = { D8_I }

+ ILD = { ~NEWR }

+ IEN = { ECT & ECR }

+ IA1 = { IEN | ILD }

+ IA2 = { ~(D1 & ILD) }

+ IB1 = { (Q1 & IEN) | ILD }

+ IB2 = { ~(D2 & ILD) }

+ IC1 = { (Q2 & Q1 & IEN) | ILD }

+ IC2 = { ~(D4 & ILD) }

+ ID1 = { (Q4 & Q2 & Q1 & IEN) | ILD }

+ ID2 = { ~(D8 & ILD) }

+ MCLK = { ~C }

+ CR = { Q8 & Q4 & Q2 & Q1 & ECR }

+ JA = { ~(ILD & IA2) & IA1 }

+ KA = { IA1 & IA2 }

+ JB = { ~(ILD & IB2) & IB1 }

+ KB = { IB1 & IB2 }

+ JC = { ~(ILD & IC2) & IC1 }

+ KC = { IC1 & IC2 }

+ JD = { ~(ILD & ID2) & ID1 }

+ KD = { ID1 & ID2 }

*

**Начало примитива PINDLY, описывающего временные задержки компонента

**Число путей равно 5, число входов разрешения – 0, число внутренних узлов – 10.

U161DLY PINDLY (5,0,10) DPWR DGND

+ CR Q1 Q2 Q4 Q8

+ C NEWR ECR NR ECT D1 D2 D4 D8 IEN

+ CR_O Q1_O Q2_O Q4_O Q8_O

+ IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+ BOOLEAN:

+ CLOCK = { CHANGED_LH(C,0) }

+ PINDLY:

+ Q1_O Q2_O Q4_O Q8_O = {

+ CASE(

+ CLOCK & NEWR!='0 & TRN_LH, DELAY(-1,13NS,20NS),

+ CLOCK & NEWR!='0 & TRN_HL, DELAY(-1,15NS,23NS),

+ CLOCK & NEWR!='1 & TRN_LH, DELAY(-1,17NS,25NS),

+ CLOCK & NEWR!='1 & TRN_HL, DELAY(-1,19NS,29NS),

+ CHANGED_HL(NR,0), DELAY(-1,26NS,38NS),

+ DELAY(-1,26NS,38NS)

+ )

+ }

+ CR_O = {

+ CASE(

+ CHANGED(ECR,0), DELAY(-1,11NS,16NS),

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.