- время удержания данных = 3 нс

Примечание: информация о параметрах взята из источника [5, раздела ТТЛ микросхем].

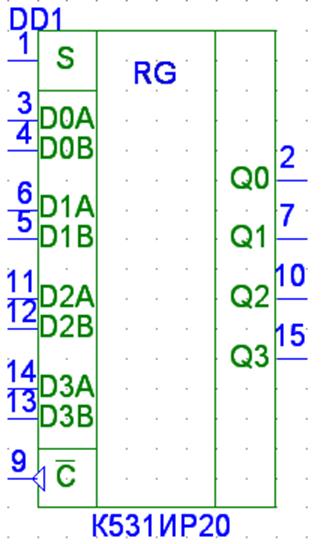

Микросхема К531ИР20

представляет собой четырехразрядный регистр с мультиплексором 2 в 1 на входе. Входы

регистра организованы как два порта данных - А и В, по четыре проводника в

каждом: D0A –

D3A и D0B - D3B. Порты данных А и B коммутируются в регистре ИР20 с помощью одноразрядного кода,

подаваемого на вход S. Если на вход S подать напряжение низкого уровня, то в регистр загружаются данные

от порта A (от входов D0A…D3A), и с

поступлением отрицательного перепада тактового импульса на вход ![]() данные появляются на выходах Q0…Q3.

данные появляются на выходах Q0…Q3.

Когда же на входе S действует напряжение высокого уровня, то, соответственно, данные в регистр загружаются через порт B (от входов D0B…D3B), и со срезом синхроимпульса поступают на выходы микросхемы.

Ниже, на рис.2, приведено условное графическое изображение проектируемого в пакете DesignLab 8.0 узла в виде иерархического символа.

Рис 2. Условное графическое изображение узла в виде иерархического символа.

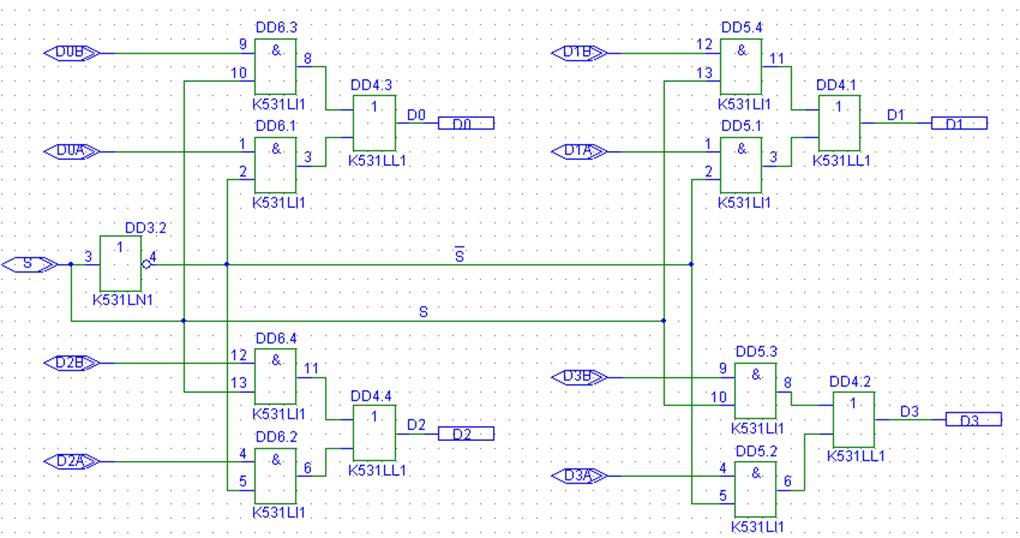

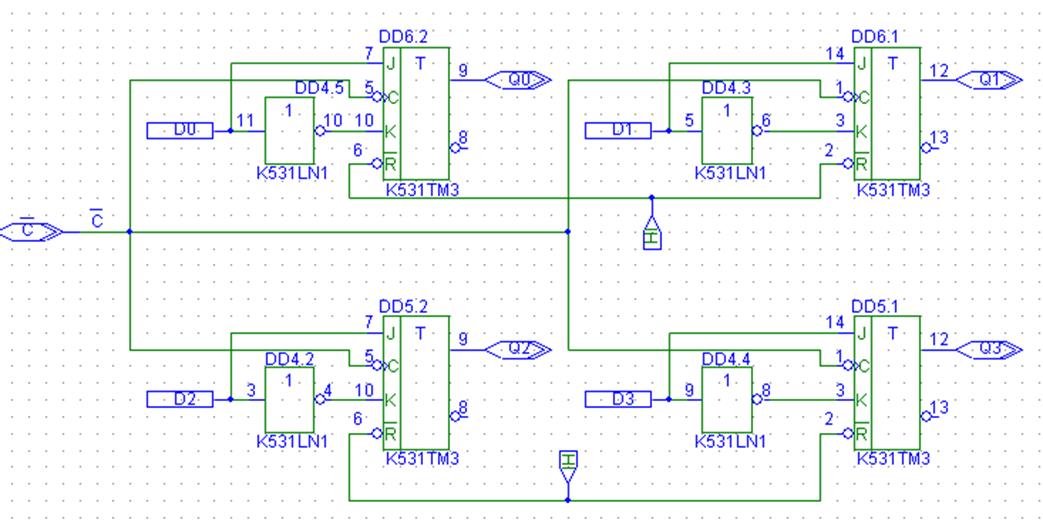

Схема замещения выполнена на элементной базе серии К531: К531LN1 – пять инверторов; К531LL1 – четыре элемента 2-ИЛИ; К531LI1 – восемь элементов 2-И и четыре JK- триггера (зарубежный аналог 7473), отечественных аналогов не имеющих, и поэтому названные K531TM3 (по ближнему брату 7474 с аналогом TM2).

На рис.3 представлена полученная схема замещения.

Рис 3. Схема замещения проектируемого узла.

Задержки элементов изменены так, чтобы соответствовать задержкам моделируемого узла (табл.3).

· Содержимое файла Schematic1.cir включает в себя информацию о моделируемой схеме в текстовом формате (подключаемые библиотеки, файл входных воздействий и т.д.).

* C:\Program Files\MSim_8\Projects\Kproject(new)\Schematic1.sch– путь к моделируемой схеме

* Schematics Version 8.0 - July 1997

* Tue Nov 29 22:17:56 2005 – дата моделирования

** Analysis setup **

.tran 20ns 2000ns – шаг моделирования и конечное время

.OPTIONS DIGINITSTATE=2

Ниже прописан путь к подключенной библиотеке:

.LIB "C:\Program Files\MSim_8\Projects\Kproject(new)\MyLIB.lib"

.STMLIB "C:\Program Files\MSim_8\Projects\Kproject(new)\Schematic1.stl" – путь к файлу с внешними воздействиями

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "nom.lib"

.INC "Schematic1.net"

.INC "Schematic1.als"

.probe

.END

· Содержимое файла Schematic1.net – содержит список цепей моделируемой схемы, в том числе и для цепей схемы замещения.

* c:\Program Files\MSim_8\Projects\Kproject\Schematic1.sch

* Schematics Version 8.0 - July 1997

* Tue Nov 22 22:17:25 2005

** Analysis setup **

.tran 20ns 1500ns

.OPTIONS DIGINITSTATE=0

.INC "C:\Program Files\MSim_8\Projects\Kproject\K531TM2.mod"

.INC "C:\Program Files\MSim_8\Projects\Kproject\K531LN1.MOD"

.INC "C:\Program Files\MSim_8\Projects\Kproject\K531LL1.mod"

.INC "C:\Program Files\MSim_8\Projects\Kproject\K531LI1.MOD"

.STMLIB "c:\Program Files\MSim_8\Projects\Kproject\Schematic1.stl"

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "nom.lib"

.INC "Schematic1.net"

.INC "Schematic1.als"

.probe

.END

* c:\Program Files\MSim_8\Projects\Kproject\Schematic1.sch

* Schematics Version 8.0 - July 1997

* Tue Nov 22 22:17:25 2005

** Analysis setup **

.tran 20ns 1500ns

.OPTIONS DIGINITSTATE=0

.INC "C:\Program Files\MSim_8\Projects\Kproject\K531TM2.mod"

.INC "C:\Program Files\MSim_8\Projects\Kproject\K531LN1.MOD"

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.