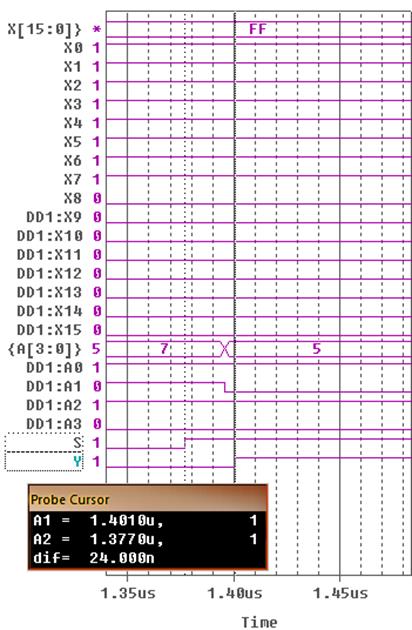

Рис.13. Задержка распространения сигнала от стробирующего входа до выхода при переключении входа из 0 в 1 (tPLH =24 нс).

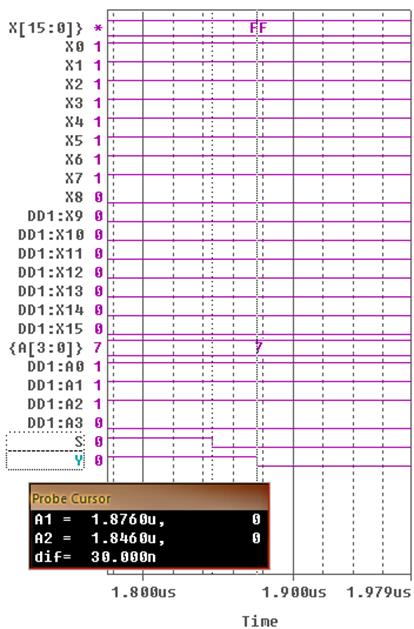

Рис.14. Задержка распространения сигнала от стробирующего входа до выхода при переключении входа из 1 в 0 (tPHL =30 нс).

Как видно из рисунков, все задержки распространения сигнала совпадают со значениями из таблицы 3.

Оценка предельных скоростных возможностей исследуемого узла подразумевает нахождение предельной частоты изменения сигналов на входах – величина, обратная максимальной задержке распространения сигнала от входа до выхода.

Вычислим минимальные частоты для каждого входа:

Информационные входы:

tmax = 20 нс;

fmin = 1 / tmax = 1 / 20нс = 40 МГц

Адресные входы:

tmax = 35 нс;

fmin = 1 / tmax = 1 / 35нс = 28,5 МГц

Стробирующий вход:

tmax = 30 нс;

fmin = 1 / tmax = 1 / 30нс = 33,3 МГц

Проверим теорию на практике, проведем временной эксперимент для стробирующего входа:

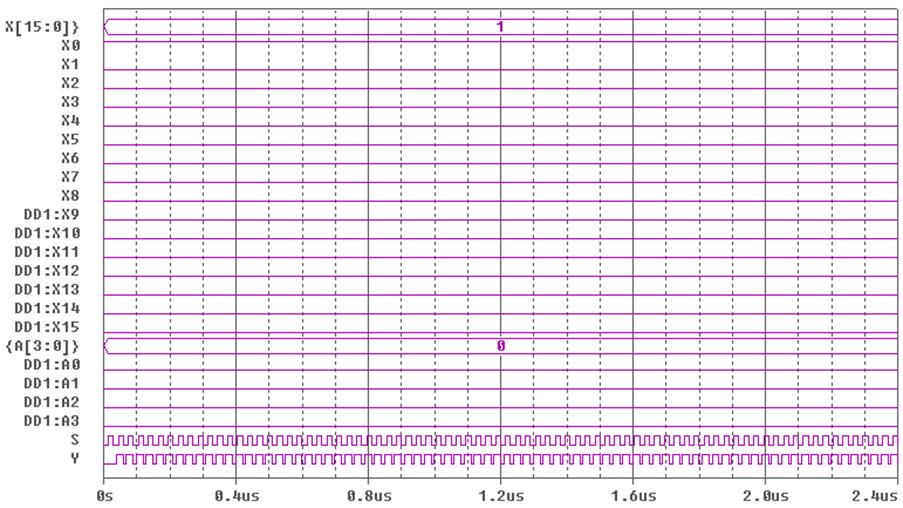

Рис.15. Работа узла при изменении стробирующего входа

Как видно из рис. 15 схема работает нормально, как и было рассчитано. Теперь проверим работу схемы на большей частоте.

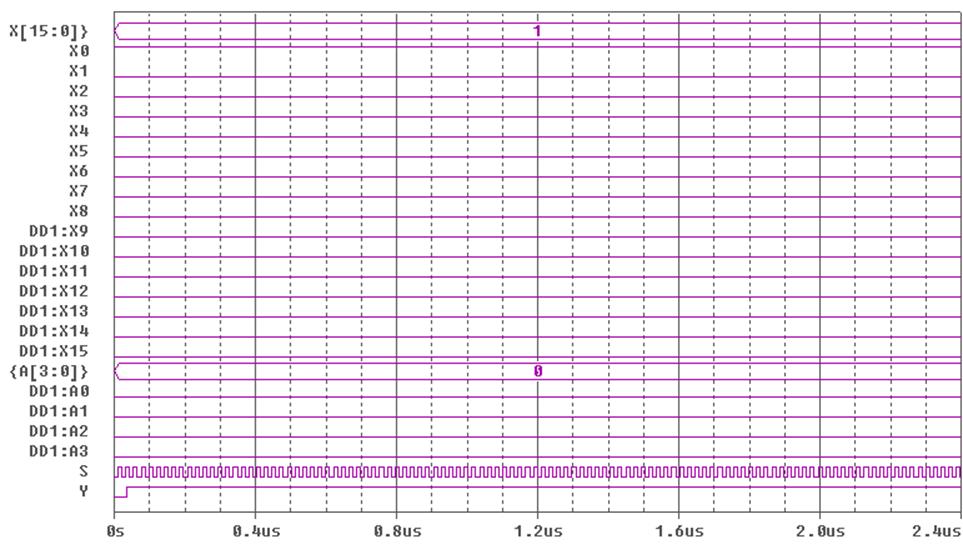

Рис.16. Работа узла при изменении стробирующего входа

Временная диаграмма работы узла при изменении сигнала S с частотой 40Мгц (большая частота взята в следствии того, что сигнал переключается в 1 быстрее, чем в 0) подтверждает наши расчеты – узел работает некорректно.

Условное графическое обозначение проектируемого узла в виде иерархического символа в PCB Simulate – проекте представлено на Рис. 15.

Рис.17 УГО моделируемого узла 155КП1 в виде иерархического символа.

Для проектирования схемы замещения использовались такие же элементы, что и для PSPICE-проекта (см. таблицу 4) . VHDL-модели элементов приведены в приложении 2.

Графические модели элементов хранятся в библиотеке kr2_vhdl.olb, VHDL модели – в файле kr_elements.vhd.

Рис.18,19. Схема замещения проектируемого узла 155КП1 на двух страницах.

Схема верификации получившегося иерархического символа в PCB Simulate – проекте показана на рис. 20.

Рис.20. Схема использования иерархического символа, созданного в PCB Simulate – проекте.

На рисунках 21-27 представлены временные диаграммы демонстрирующие правильность работы узла и соответствие задержек реальным.

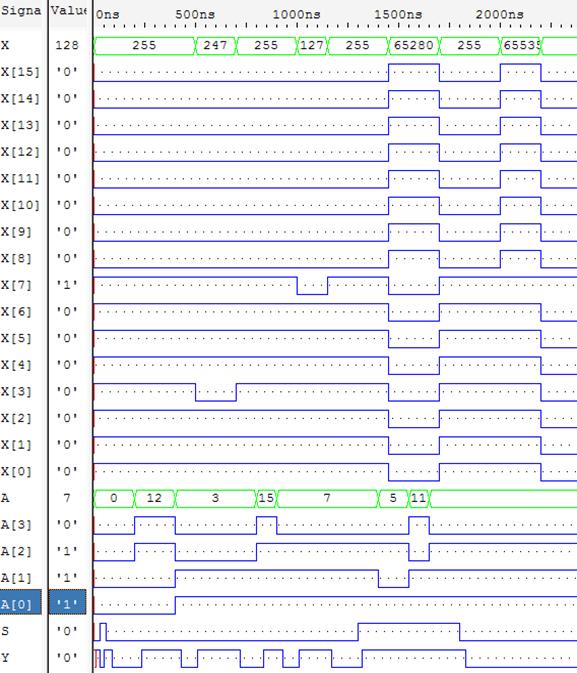

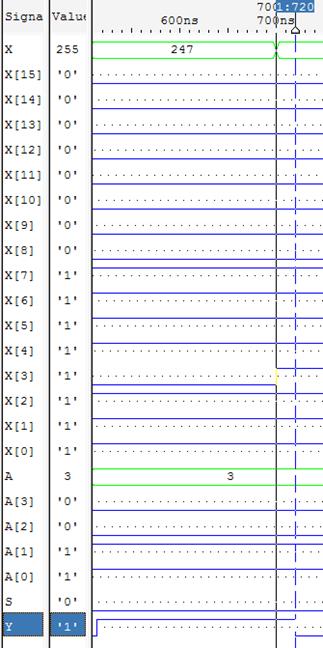

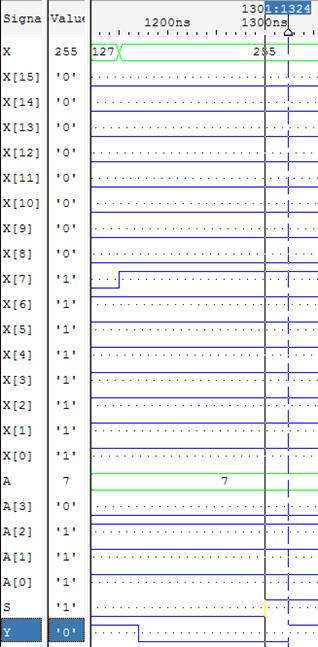

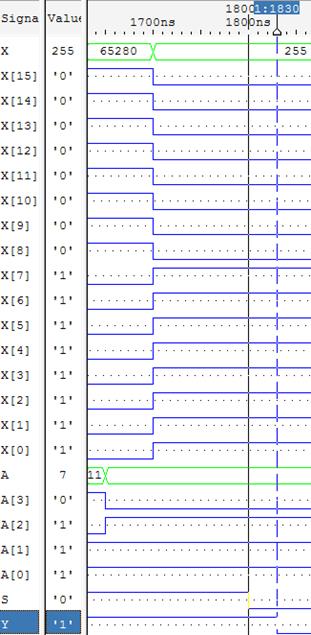

Рис.21. Временная диаграмма работы проектируемого узла

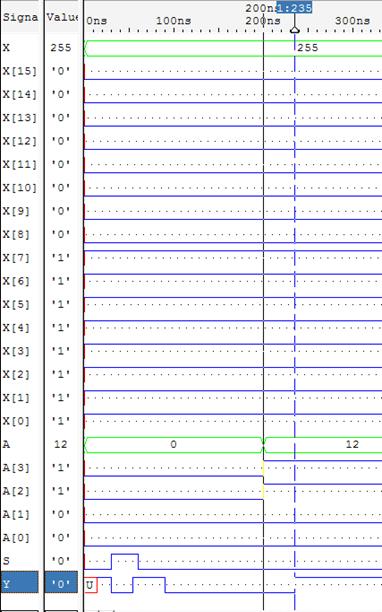

Рис.22. Задержка распространения сигнала от адресного входа до выхода при переключении входа из 0 в 1 (tPLH =35 нс).

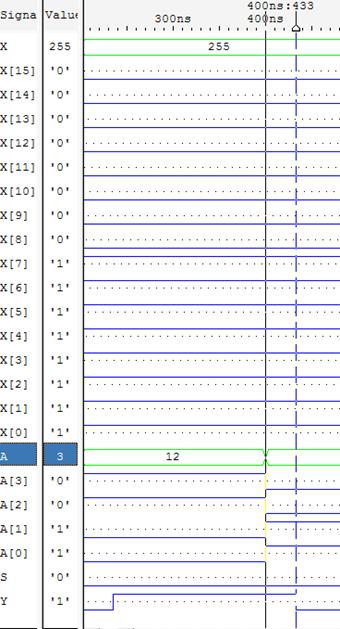

Рис.23. Задержка распространения сигнала от адресного входа до выхода при переключении входа из 1 в 0 (tPHL =33 нс).

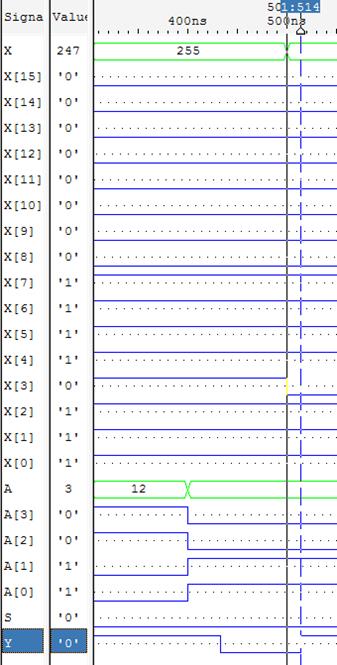

Рис.24. Задержка распространения сигнала от информационного входа до выхода при переключении входа из 0 в 1 (tPLH =14 нс).

Рис.25. Задержка распространения сигнала от информационного входа до выхода при переключении входа из 1 в 0 (tPHL=20 нс).

Рис.26. Задержка распространения сигнала от стробирующего входа до выхода при переключении входа из 0 в 1 (tPLH =24 нс).

Рис.27. Задержка распространения сигнала от стробирующего входа до выхода при переключении входа из 1 в 0 (tPHL =30 нс).

Проанализировав результаты моделирования PSPICE и PCB Simulate проектов, можно сделать вывод о том, что спроектированный узел в обоих режимах работает одинаково, с теми же задержками.

Графические изображения элементов в обоих проектах создаются одинаково, функциональные модели же строятся совершенно по-разному: в PCB Simulate проекте создание собственных моделей (на языке VHDL) проходит гораздо проще, чем в PSPICE.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.