Кафедра вычислительной техники

|

Курсовая работа

по дисциплине «Моделирование»

Проектирование цифрового автомата в системе сквозного проектирования DesignLab 8.0 и OrCad 9.1

|

Выполнил: Студент АВТ Группы АМ-010 Безлер Игорь |

Проверил: Шалагинов А. В. |

Содержание. 2

Постановка задачи. 3

УГО моделируемого узла, таблица назначения выводов. 3

Логическая таблица режимов работы. 4

Таблица реальных задержек. 4

Временные соотношения для КР1533ИР8. 4

Описание работы моделируемого узла. 4

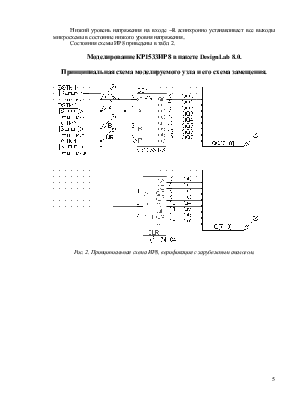

Моделирование КР1533ИР8в пакете DesignLab 8.0. 5

Принципиальная схема моделируемого узла и его схема замещения. 5

Макро модели вентилей. 7

Текстовое Spice-описание моделируемого узла. 8

Содержимое файла описания внешних воздействий. 10

Результаты моделирования схемы замещения в пакете DesignLab 8.0. 11

Определение максимальной частоты работы ИР8. 12

Создание функциональной модели КР1533ИР8. 13

Функциональное описание моделируемого узла. 13

Результаты работы функциональной модели. 15

Контроль временных соотношений. 16

Моделирование КР1533ИР8 в пакете OrCAD 9.1. 19

Принципиальная схема моделируемого узла и его схема замещения. 19

VHDL модели вентилей схемы замещения. 21

Результаты работы схемы замещения. 24

Поведенческая модель узла. 26

Результаты работы поведенческой модели КР1533ИР8. 28

Выводы. 30

Список используемой литературы. 31

Дана микросхема КР1533ИР8 – представляет собой восьмиразрядный сдвиговый регистр с последовательной загрузкой и параллельной выгрузкой. Требуется создать ее структурные и поведенческие модели в пакетах OrCAD 9.1 и DesignLab 8.0 и провести имитационные эксперименты с разработанным узлом, с целью подтверждения работоспособности узла, определения максимально-допустимой частоты работы и соответствия временных задержек требуемым.

Рис. 1. УГО и цоколевка микросхемы КР1533ИР8

|

№ вывода |

Обозначение |

Назначение |

|

1 |

A |

Вход данных 1 |

|

2 |

B |

Вход данных 2 |

|

3 |

Q0 |

Выход данных 1 |

|

4 |

Q1 |

Выход данных 2 |

|

5 |

Q2 |

Выход данных 3 |

|

6 |

Q3 |

Выход данных 4 |

|

7 |

GND |

«Земля» |

|

8 |

C |

Вход тактирования |

|

9 |

~R |

Вход сброса |

|

10 |

Q4 |

Выход данных 5 |

|

11 |

Q5 |

Выход данных 6 |

|

12 |

Q6 |

Выход данных 7 |

|

13 |

Q7 |

Выход данных 8 |

|

14 |

PWR |

«Питание» |

Табл. 1. Назначение выводов микросхемы ИР8

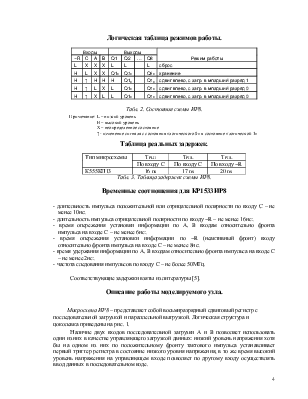

|

Входы |

Выходы |

Режим работы |

||||||

|

~R |

C |

A |

B |

Q1 |

Q2 |

… |

Q8 |

|

|

L |

X |

X |

X |

L |

L |

L |

сброс |

|

|

H |

L |

X |

X |

Q10 |

Q20 |

Q80 |

хранение |

|

|

H |

↑ |

H |

H |

H |

Q10 |

Q70 |

сдвиг влево, с загр. в младший разряд 1 |

|

|

H |

↑ |

L |

X |

L |

Q10 |

Q70 |

сдвиг влево, с загр. в младший разряд 0 |

|

|

H |

↑ |

X |

L |

L |

Q10 |

Q70 |

сдвиг влево, с загр. в младший разряд 0 |

|

Табл. 2. Состояния схемы ИР8.

|

Примечание: L – низкий уровень H – высокий уровень X – неопределенное состояние ↑ - изменение сигнала с состояния «логического 0» в состояние «логической 1» |

|

Тип микросхемы |

TPLH |

TPHL |

TPHL |

|

По входу C |

По входу C |

По входу ~R |

|

|

К555КП13 |

16 ns |

17 ns |

20 ns |

Табл. 3. Таблица задержек схемы ИР8.

Временные соотношения для КР1533ИР8

- длительность импульса положительной или отрицательной полярности по входу С – не менее 10нс;

- длительность импульса отрицательной полярности по входу ~R – не менее 16нс;

- время опережения установки информации по A, B входам относительно фронта импульса на входе C – не менее 6нс;

- время опережения установки информации по ~R (неактивный фронт) входу относительно фронта импульса на входе C – не менее 8нс;

- время удержания информации по A, B входам относительно фронта импульса на входе C – не менее 2нс;

- частота следования импульсов по входу C – не более 50МГц.

Соответствующие задержки взяты из литературы [5].

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.