**Логический блок. Здесь зашита функциональность элемента

U1 BUFA(4) DPWR DGND

+ RBAR_I C_I A_I B_I RBAR C A B

+ D0_GATE IO_STD IO_LEVEL={IO_LEVEL}

*

U2 AND(2) DPWR DGND

+ A B IN

+ D0_GATE IO_STD

*

U3 DFF(8) DPWR DGND

+ $D_HI RBAR C

+ IN Q0 Q1 Q2 Q3 Q4 Q5 Q6

+ Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

+ $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC

+ D0_EFF IO_STD

*

** Блок задержек. Он отвечает за моделируемые временные задержки

U164DLY PINDLY (8,0,4) DPWR DGND

+ Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

+ RBAR C A B

+ Q0_O Q1_O Q2_O Q3_O Q4_O Q5_O Q6_O Q7_O

+ IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+ PINDLY:

+ Q0_O Q1_O Q2_O Q3_O Q4_O Q5_O Q6_O Q7_O = {

+ CASE(

+ CHANGED_LH(C,0) & TRN_LH, DELAY(16NS,16NS,16NS),

+ CHANGED_LH(C,0) & TRN_HL, DELAY(17NS,17NS,17NS),

+ CHANGED_HL(RBAR,0) & TRN_HL, DELAY(-1,20NS,20NS),

+ DELAY(16NS,17NS,20NS) ;DEFAULT

+ )

+ }

+

+ FREQ:

+ NODE = C

+ MAXFREQ = 50MEG

+

+ WIDTH:

+ NODE = C

+ MIN_HIGH = 10NS

+ MIN_LOW = 10NS

+

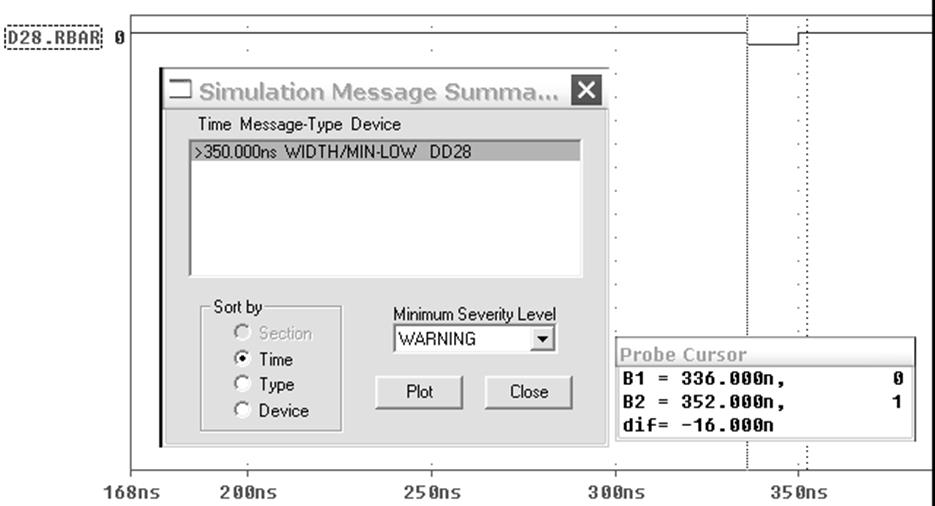

+ WIDTH:

+ NODE = RBAR

+ MIN_LOW = 16NS

+

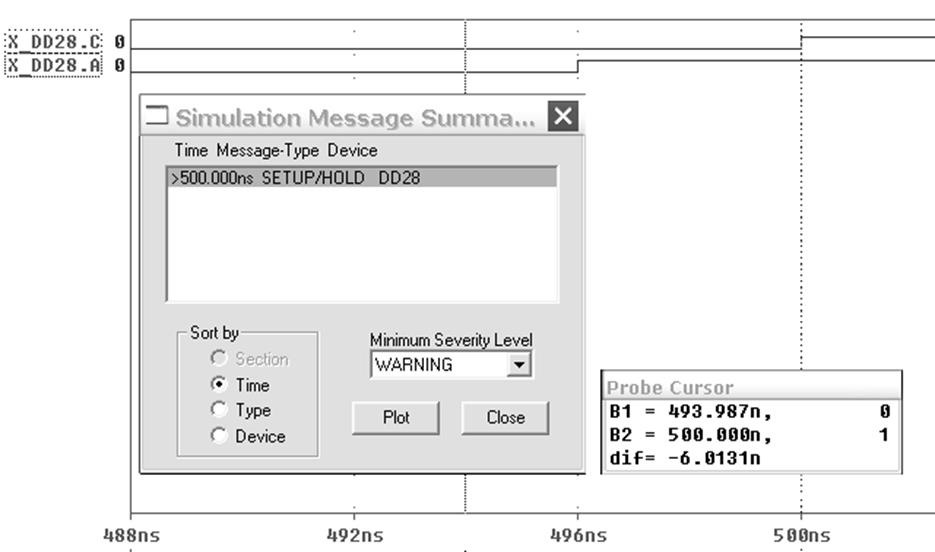

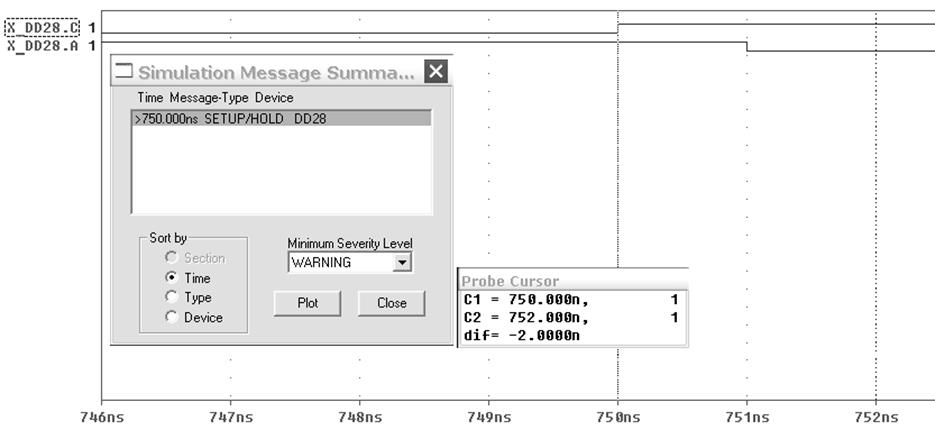

+ SETUP_HOLD:

+ CLOCK LH = C

+ DATA(2) A B

+ SETUPTIME = 6NS

+ HOLDTIME = 2NS **

+ AFFECTS_ALL

+ WHEN = { RBAR != '0 }

+

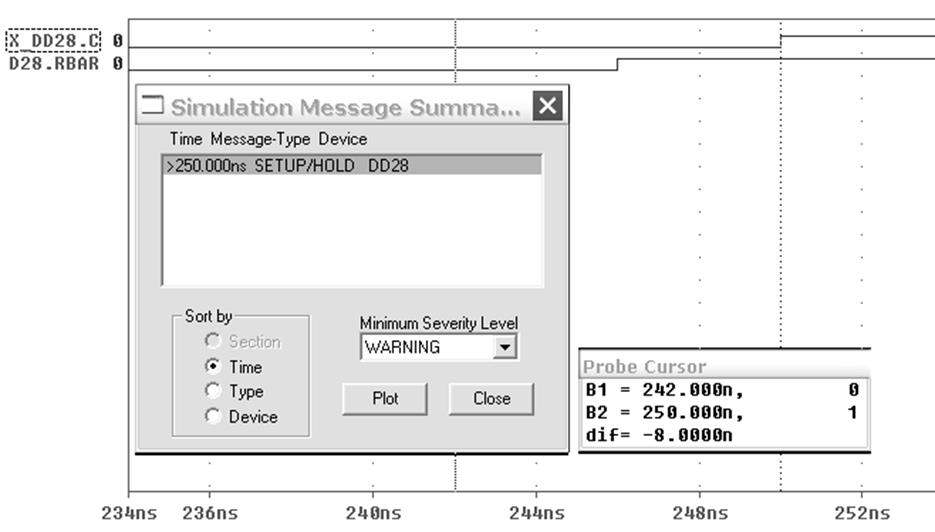

+ SETUP_HOLD:

+ DATA(1) RBAR

+ CLOCK LH = C

+ RELEASETIME_LH = 8NS

+ AFFECTS_ALL

*

.ENDS

*

*$

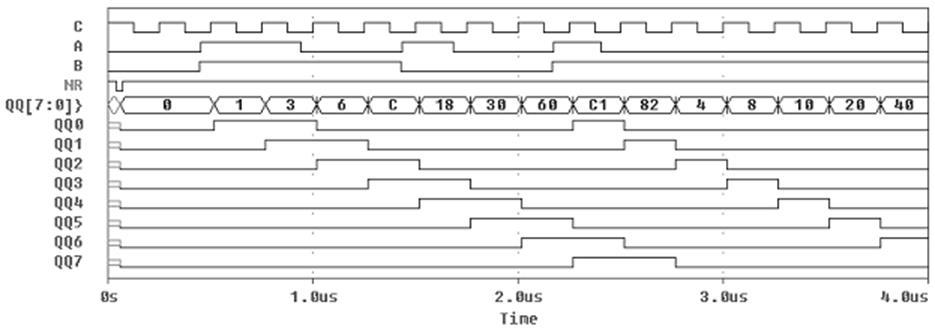

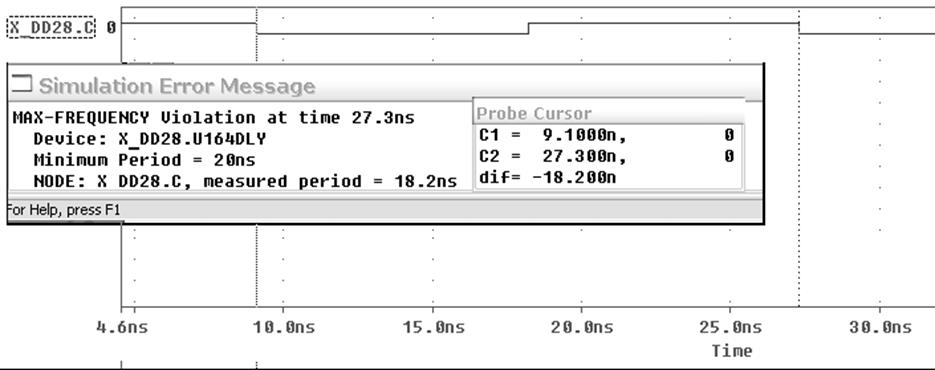

Рис. 11. График из постпроцессора моделирования.

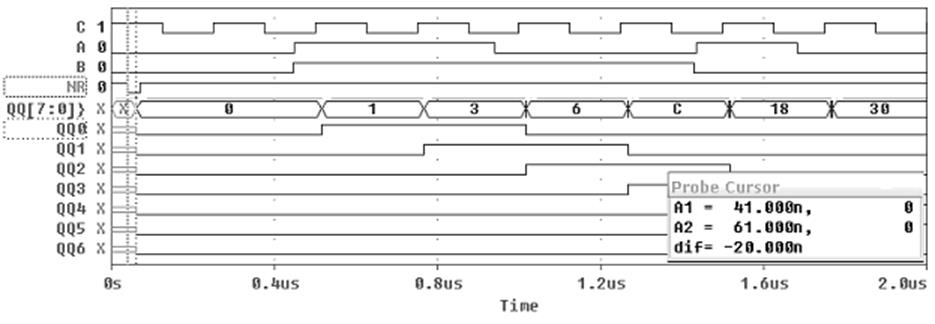

Рис. 12. Задержка распространения сигнала от входа ~R до выходов

при переключении из 1 в 0 – 20 нс.

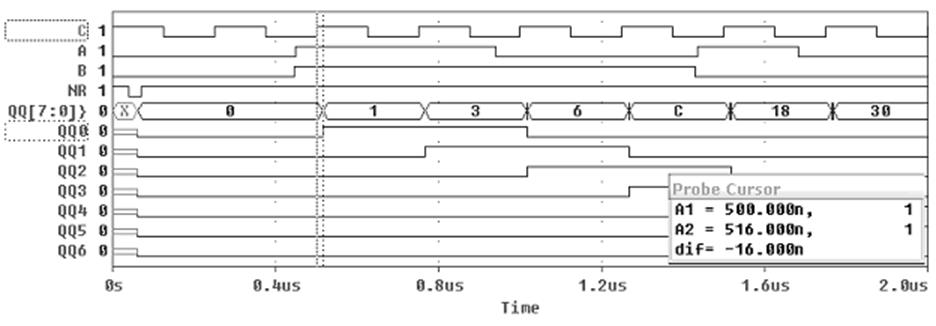

Рис. 13. Задержка распространения сигнала от входа С до выходов

при переключении из 0 в 1 – 16 нс.

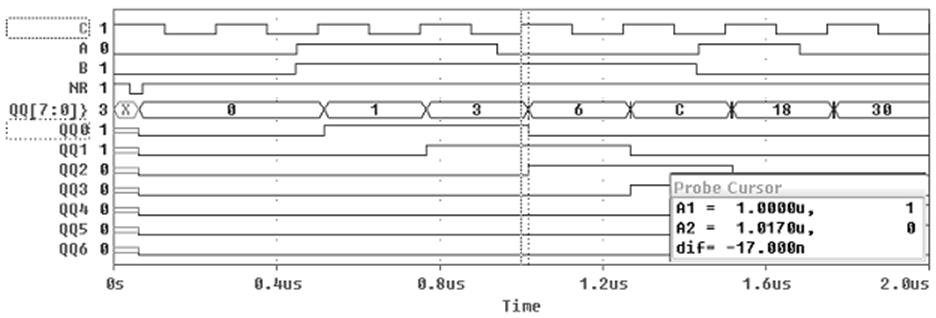

Рис. 14. Задержка распространения сигнала от входа С до выходов

при переключении из 1 в 0 – 17 нс.

Контроль временных соотношений

Рис 15. Время предустановки данных на входе A относительно импульса C

Рис 16. Минимальное время длительности сигнала NR

Рис 17. Минимальное время длительности сигнала NR

Рис 18. Время опережения установки по NR относительно фронта импульса на входе C

Рис 19. Максимальная частота работы регистра ИР8

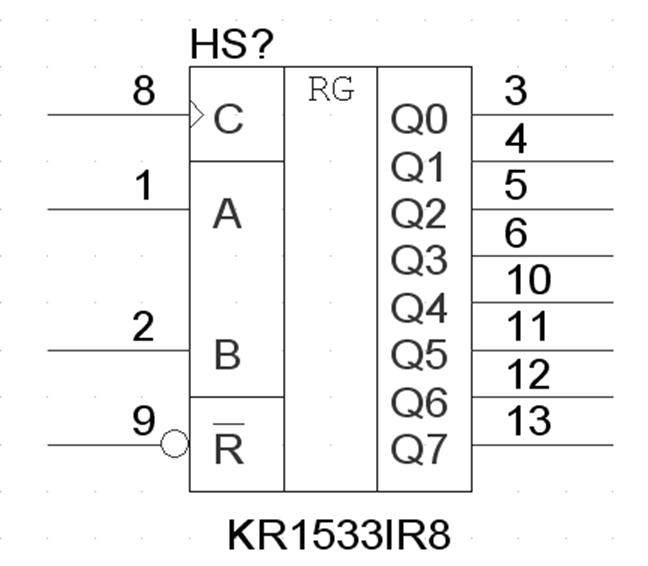

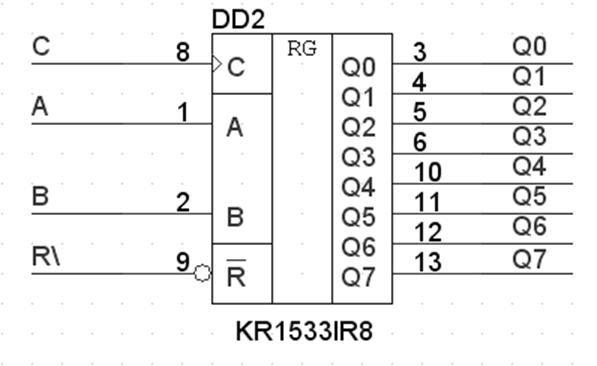

Моделирование КР1533ИР8 в пакете OrCAD 9.1.

УГО моделируемого узла.

Рис. 20. УГО КР1533ИР8.

Рис. 21. Принципиальная схема ИР8.

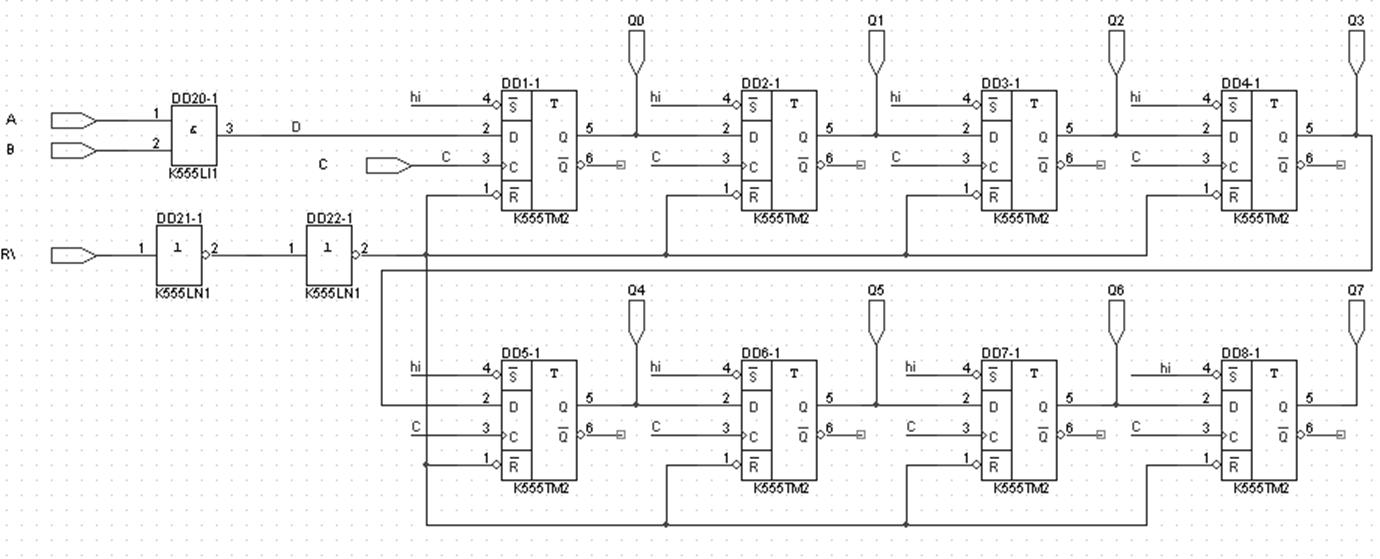

Рис. 22. Схема замещения ИР8.

Основу схемы замещения составили те же вентили, которые использовались при проектировании схемы замещения в DesignLab . Cозданные модели вентилей не соответствуют реальным элементам по динамическим характеристикам. Характеристики были подобраны таким образом, чтоб проектируемый нами элемент работал правильно. Ниже приведены VHDL-модели для данных вентилей.

Так как в один корпус ИМС входит несколько вентилей, то приходилось копировать одно и тоже описание для разных секций ИМС. Хорошо, что у Оркада очень удобно задавать упаковочную информацию.

---Описание входов и выходов микросхемы, а также контактов питания и земли---

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.