Новосибирский Государственный Технический Университет

Кафедра вычислительной техники

Расчетно-графическая работа

По дисциплине «Схемотехника»

«Проектирование модуля памяти»

Работу выполнил: Работу проверил:

Факультет: АВТ Соболев В. И.

Группа: АМ-210

Студент: Третьяков М.Л.

Новосибирск, 2004

Требуется построить запоминающее устройство, состоящее из оперативной памяти SRAM и постоянной EPROM.

Разрядность шин адреса и данных 32, емкостная нагрузка на шины не более 8 pF. Время цикла записи и чтения не более 100 нс.

Для SRAM выбирается микросхема СУМ1241В фирмы Sypress с организацией (256К x 32).

Для EPROM выбираем микросхему СУ27С128 с организацией (16К x8), той же фирмы изготовителя в

Параметры всех используемых микросхем можно посмотреть в приложении.

Исходя из требуемой емкости памяти, определяем:

SRAM 1Мбайт = 223 бит = nслов* 32; nслов = 218 =256 К следовательно организация требуемой памяти имеет вид ( 256К x 32 ) .

EPROM 64 Кбайта =219 бит = nслов*32; nслов = 214 = 16К организация памяти ( 16К x 32 ).

Число микросхем считается по формуле:

где N – информационная емкость, n – разрядность

В данном случае получаем: Q=1*1=1, для SRAM и Q=1*4=4, для EPROM.

Для этого необходимо произвести следующие расчеты:

Определяем коэффициенты объединения микросхем:

SRAM – KобА = ( Nмод / Nбис )*(nмод / nбис ) = 1 Коб DQ =( Nмод / Nбис )=1;

EPROM – КобА=(16/16)*32 / 8= 4 Коб DQ = 1;

Следовательно суммарный КобА=5, Коб DQ = 2

Определим нагрузку на шине адреса и данных:

СнагрА = СIn КобА + Смонтажа = 16*5 +20 = 100 пФ.

СнагрDQ = Сout* ( Коб DQ – 1) +Смонтажа =16*1 +20 = 36пФ.

Для согласования микросхем с шинами необходима установка буферов, для чего выбираем:

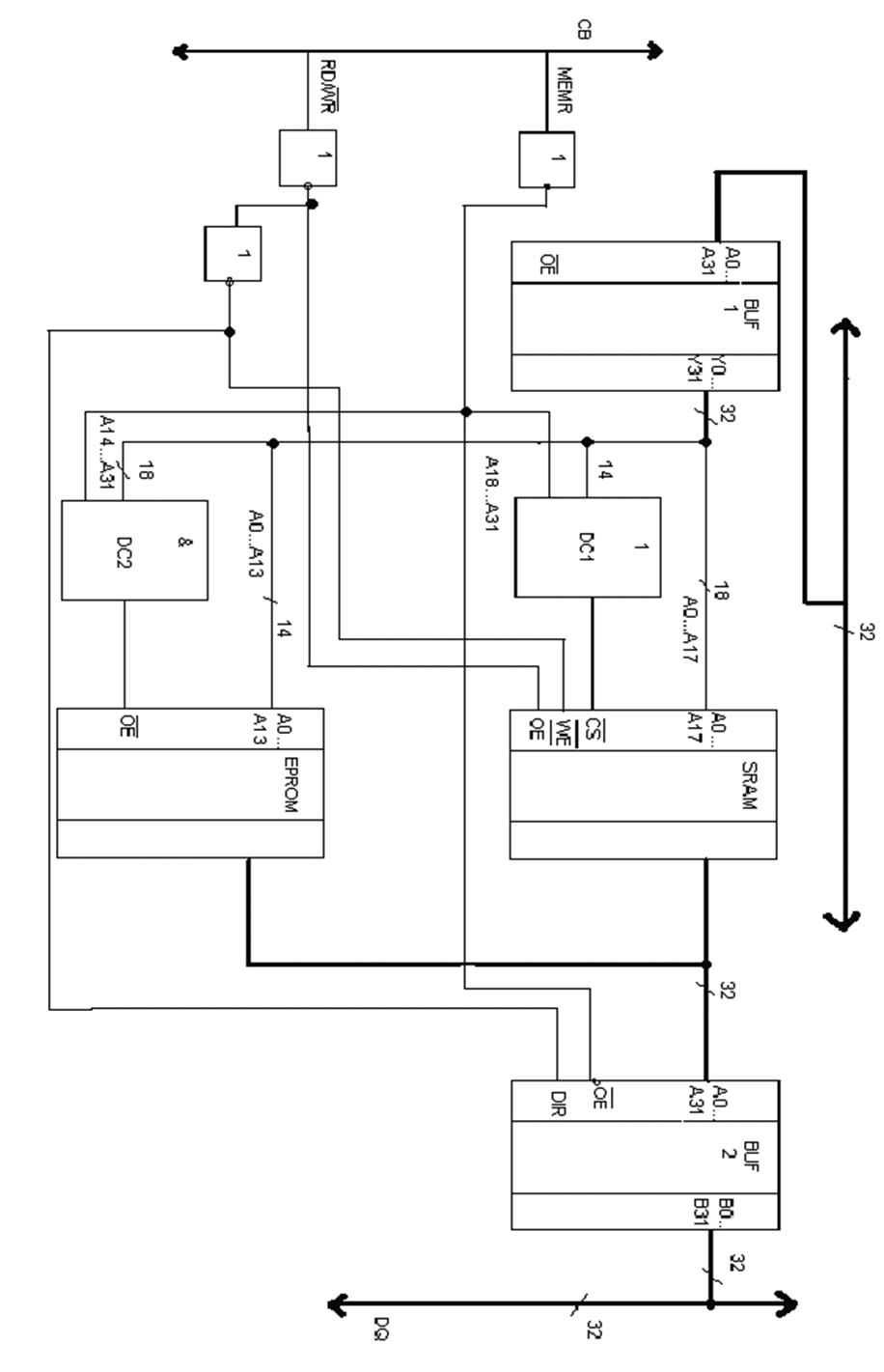

Функциональная схема данного накопителя изображена на рисунке 1

Открывание буферных микросхем производится высоким уровнем сигнала MEMR шины управления через инвертор.

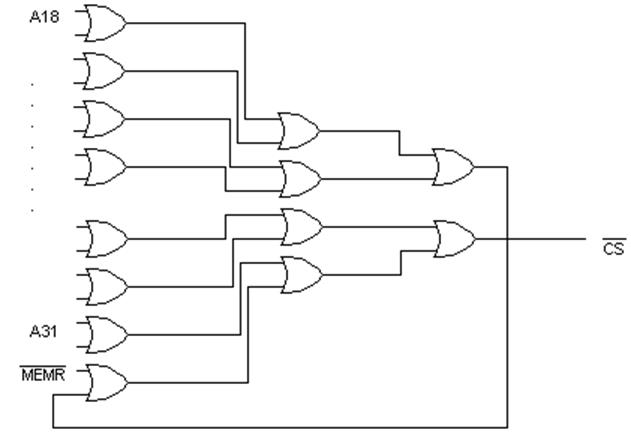

Для выбора типа памяти все адресное пространство, состоящие из 232 слов может быть разбито на страницы, каждая из которых содержит 214 слов. Тогда все пр-во будет состоять из 218 страниц. При таком разделении SRAM будет содержать 24 страниц, а EPROM разместится на одной странице. Для удобства дешифрирования для SRAM выделяем первые 16 страниц, характерные тем, что старшие не информационные 14 разрядов адресного пространства имеют низкий уровень ,что можно использовать для приведения микросхемы SRAM в активное состояние, т.е. CSsram= ØA18 Ù… Ù ØA31;

ØCS= A18 Ú…Ú A31.

Для построения логической организации ØCS используется микросхема 4 – 2 ИЛИ типа

КР1554ЛЛ1

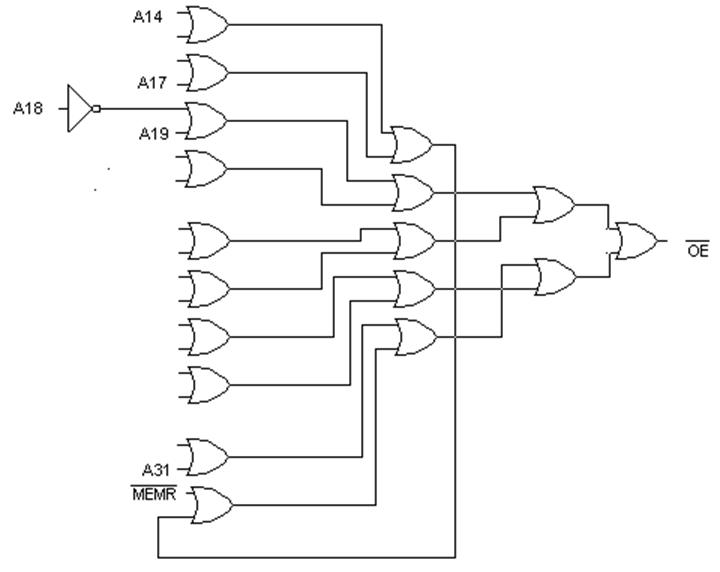

Для EPROM удобно использовать последнюю страницу, в которой старшие не информационные 18 разрядов находятся на высоком уровне, эту комбинацию можно использовать для активизации микросхемы т.е. OEeprom = A14 Ù … ÙA31 ØOE= ØA14Ú…ÚØA31

Для построения организации ØOE используется микросхема 2-4 И типа КР1554ЛИ6.

Сигналом RD/ØWR с шины управления выбирается режим чтения или записи микросхем SRAM и BUF2. при высоком уровне этого сигнала через инвертор активизируются входы ØOE SRAM , ØOE и DIR BUF2( чтение ). При низком уровне через инверторы активизируются ØWR SRAM, для BUF2 низкий уровень соответствует режиму записи.

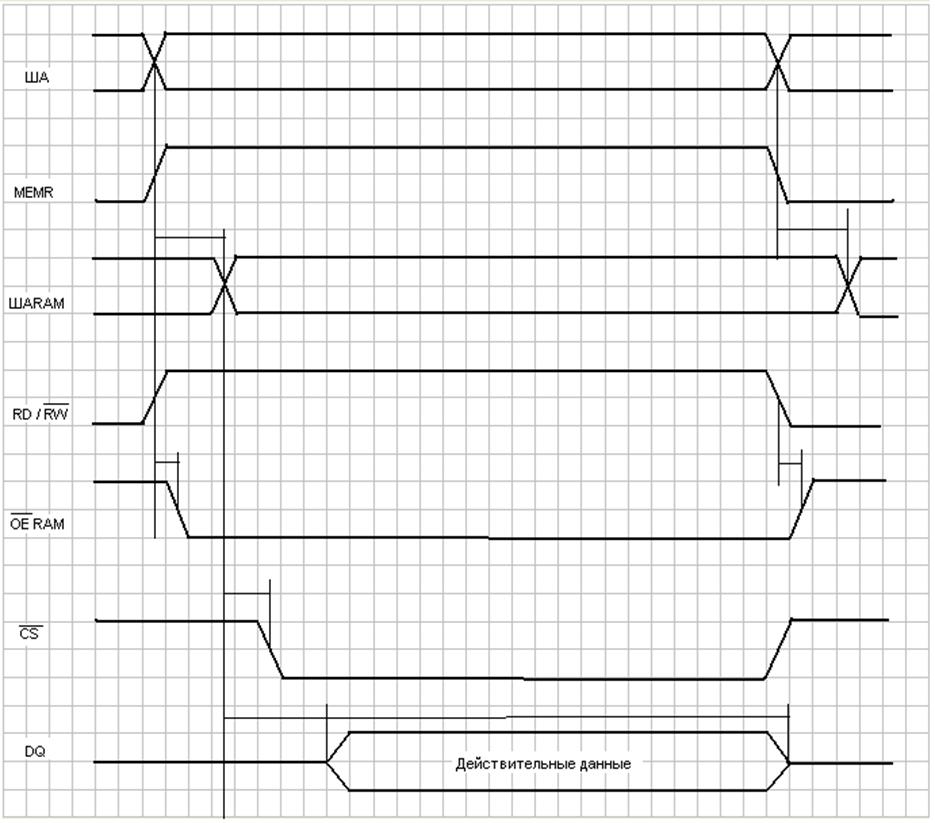

Чтение с SRAM:

Временные диаграммы соответствующие циклу чтения с SRAM изображены на рисунке 2.

tRC = tBA + tчт =45

Tц= tи + tBUF1 + tD1 + tBA + tчт= 7 + 8 + 4 * 7.5 + 45 = 90

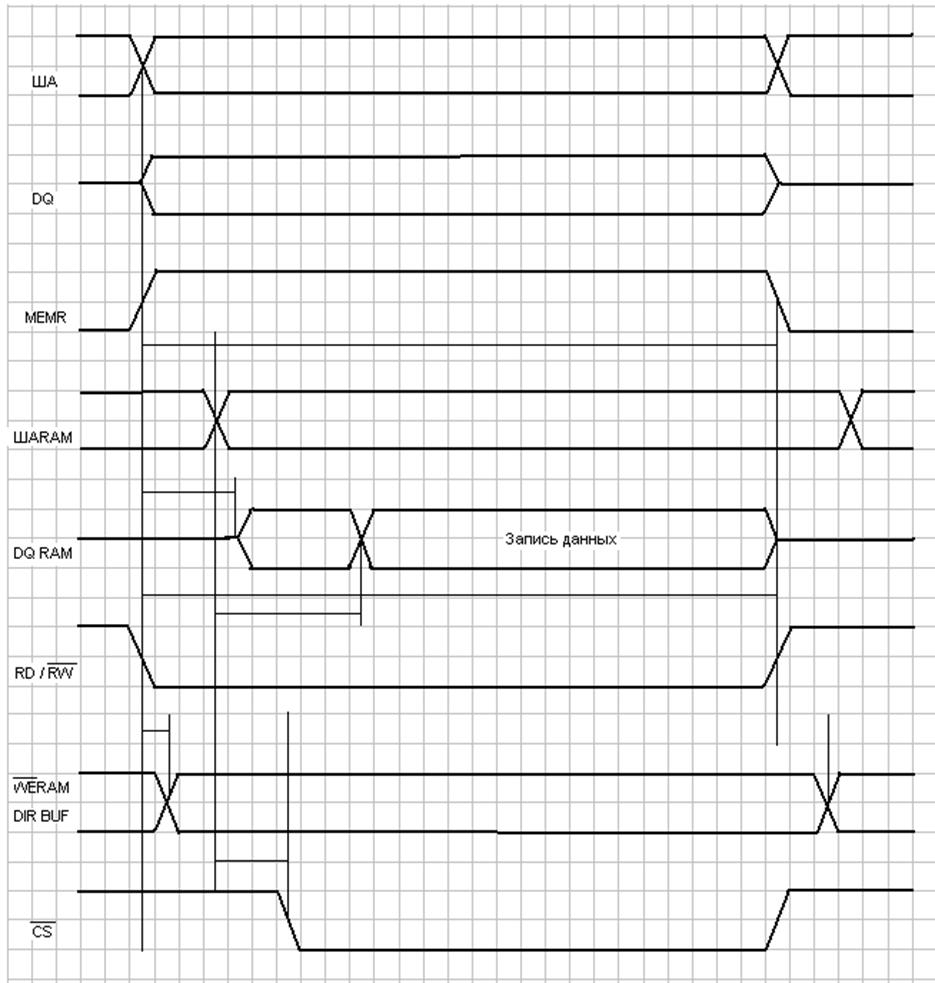

Запись на SRAM:

Временные диаграммы, соответствующие циклу записи на SRAM изображены на рисунке 3

t1=tи+ tBUF1 t2=2*tи+tBUF2

tBA + tзап = t WC = 25нс

Tц = tи + tBUF1 + tD1 + tBA + tзап= 7 + 8 + 4 * 7.5 + 25 = 70нс

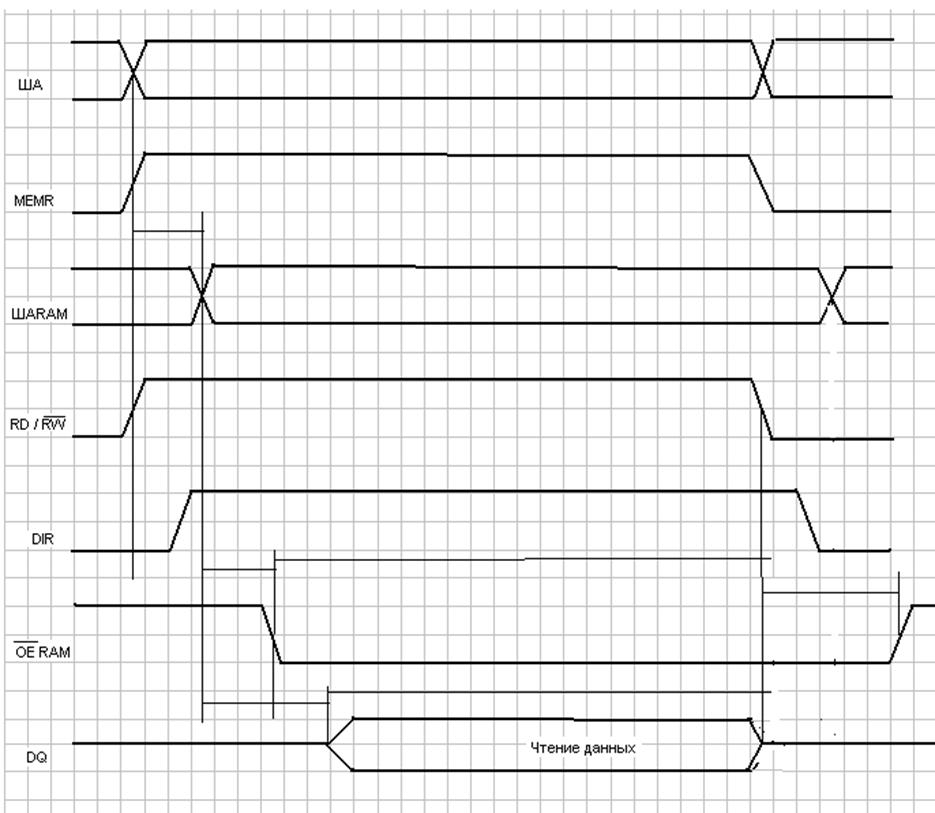

Чтение с EPROM:

Временные диаграммы соответствующие циклу чтения с EPROM изображены на рисунке 4

tBA + tчт = tHZCE

t1=tи+tBUF1

Tц= tи+ tBUF1 + tD2 + tBA + tчт= 9 + 8 + 4*8.5 + 9 +20 = 80

Рис.1 Электрическая схема DC1 на базе КР1554ЛЛ1.

Рис.2 Электрическая схема DC2 на базе КР1554ЛЛ1 и КР1554ЛН1.

Рис 3

Рис.4 Временные диаграммы чтения с SRAM

t PLH_1- время переключения буфера.

t PLH_2- время переключения инвертора

t PLH_3- время переключения DC1

t AA- время выборки адреса

t RC- время наличия адреса SRAM в цикле

T ц – время цикла работы ЗУ.

T ц = t PLH_1+ t RC =6.5+45=51.5

Рис 5 Запись в SRAM

t PLH_1- время переключения буфера.

t PLH_2- время переключения инвертора

t PLH_3- время переключения DC1

t AA- время выборки адреса

t WC- время наличия адреса SRAM в цикле

T ц – время цикла работы ЗУ.

T ц = t PLH_1+ t WC =6.5+45=51.5

Рис 6 Чтение с EPROM

t PLH_1- время переключения буфера.

t PLH_2- время переключения инвертора

t PLH_3- время переключения DC2

t AA- время выборки адреса

t HZCE – от начала OE до конца DQ

T ц – время цикла работы ЗУ.

T ц = t PLH_1+ t PLH_3 +tHZCE= 6.5 + 4*8.5 + 9 +20=69.5

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.