а ) Сдвиг влево. Реализуется после активизации SL(входа разрешения “сдвига вправо”), установки SEMO0 в нуль, и высокого уровня SEMO1.

б) Режим установки и удержания логического нуля,

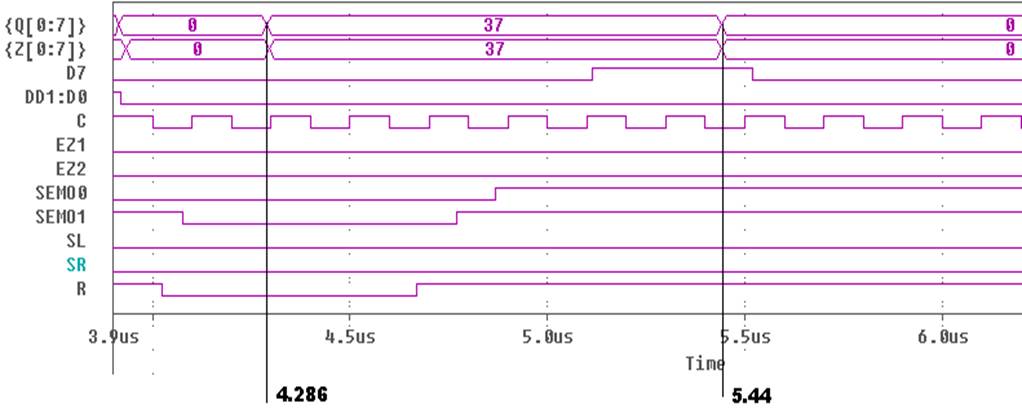

Рис 6.Загрузка.

На рис. 5, с помощью временных диаграмм наглядно представлен режим загрузки и последующая установка в нуль.

8. Оценка предельных скоростных возможностей исследуемого узла.

Для оценки скоростных возможностей узла я постепенно увеличивал частоту тактирующего сигнала C в результате чего на частоте 14 MHz появились ошибки.

9. Функциональное описание проектируемого узла.

Задержки «заложенные» в макромодель идентичны задержкам, измеренным на принципиальной схеме узла.

.SUBCKT Register3 CLK_I CLRBAR_I SEMO1_I SEMO0_I G1BAR_I G2BAR_I SL_I SR_I

+ ZD0_B ZD1_B ZD2_B ZD3_B ZD4_B ZD5_B ZD6_B ZD7_B D0_O D7_O

+ OPTIONAL: PWR=$G_DPWR GND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

URegister3LOG LOGICEXP(32,25) PWR GND

+ CLK_I CLRBAR_I SEMO1_I SEMO0_I G1BAR_I G2BAR_I SL_I SR_I

+ ZD0_B ZD1_B ZD2_B ZD3_B ZD4_B ZD5_B ZD6_B ZD7_B ; BUFFERING

+ LZD0 LZD1 LZD2 LZD3 LZD4 LZD5 LZD6 LZD7

+ ZD0 ZD1 ZD2 ZD3 ZD4 ZD5 ZD6 ZD7

+

+ C CLRBAR SEMO1 SEMO0 G1BAR G2BAR SL SR

+ ZD0 ZD1 ZD2 ZD3 ZD4 ZD5 ZD6 ZD7

+ D1A D1B D1C D1D D1E D1F D1G D1H OE

+ D0_GATE IO_ALS00

+ IO_LEVEL={IO_LEVEL}

+ LOGIC:

+

* BUFFERING:

+ C = { CLK_I }

+ CLRBAR = { CLRBAR_I }

+ SEMO1 = { SEMO1_I }

+ SEMO0 = { SEMO0_I }

+ G1BAR = { G1BAR_I }

+ G2BAR = { G2BAR_I }

+ SL = { SL_I }

+ SR = { SR_I }

+ ZD0 = { ZD0_B }

+ ZD1 = { ZD1_B }

+ ZD2 = { ZD2_B }

+ ZD3 = { ZD3_B }

+ ZD4 = { ZD4_B }

+ ZD5 = { ZD5_B }

+ ZD6 = { ZD6_B }

+ ZD7 = { ZD7_B }

+

* INTERMEDIATE TERMS:

+ SA = { ~(SEMO0 | ~CLRBAR) }

+ SB = { ~(SA | ~CLRBAR) }

+

+ S0S1 = { SB & SEMO1 }

+ S0/S1 = { SB & ~SEMO1 }

+ /S0S1 = { SA & SEMO1 }

+ /S0/S1 = { SA & ~SEMO1 }

+

* OUTPUTS:

+ D1A = { (S0/S1 & SR ) | (/S0S1 & LZD1) | (S0S1 & ZD0)

+ | (/S0/S1 & LZD0) }

+ D1B = { (S0/S1 & LZD0) | (/S0S1 & LZD2) | (S0S1 & ZD1)

+ | (/S0/S1 & LZD1) }

+ D1C = { (S0/S1 & LZD1) | (/S0S1 & LZD3) | (S0S1 & ZD2)

+ | (/S0/S1 & LZD2) }

+ D1D = { (S0/S1 & LZD2) | (/S0S1 & LZD4) | (S0S1 & ZD3)

+ | (/S0/S1 & LZD3) }

+ D1E = { (S0/S1 & LZD3) | (/S0S1 & LZD5) | (S0S1 & ZD4)

+ | (/S0/S1 & LZD4) }

+ D1F = { (S0/S1 & LZD4) | (/S0S1 & LZD6) | (S0S1 & ZD5)

+ | (/S0/S1 & LZD5) }

+ D1G = { (S0/S1 & LZD5) | (/S0S1 & LZD7) | (S0S1 & ZD6)

+ | (/S0/S1 & LZD6) }

+ D1H = { (S0/S1 & LZD6) | (/S0S1 & SL ) | (S0S1 & ZD7)

+ | (/S0/S1 & LZD7) }

+ OE = { G1BAR | G2BAR | (SEMO1 & SEMO0) }

*

U1 DFF(8) DPWR DGND $D_HI CLRBAR C

+ D1A D1B D1C D1D D1E D1F D1G D1H

+ LZD0 LZD1 LZD2 LZD3 LZD4 LZD5 LZD6 LZD7

+ $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC

+ D0_EFF IO_ALS00

*

URegister3DLY PINDLY (10,1,17) PWR GND

+ LZD0 LZD1 LZD2 LZD3 LZD4 LZD5 LZD6 LZD7 LZD0 LZD7

+ OE

+ G1BAR G2BAR C CLRBAR SEMO1 SEMO0 SEMO0 ZD0 ZD1 ZD2 ZD3 ZD4 ZD5 ZD6 ZD7 SR SL

+ ZD0_B ZD1_B ZD2_B ZD3_B ZD4_B ZD5_B ZD6_B ZD7_B D0_O D7_O

+ IO_ALS00 MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+

+ BOOLEAN:

+ ENABLE1 = { G1BAR!='1 & G2BAR!='1 }

+ ENABLE2 = { SEMO1!='1 | SEMO0!='1 }

+ DISABLE1 = { G1BAR!='0 | G2BAR!='0 }

+ DISABLE2 = { SEMO1!='0 & SEMO0!='0 }

+ CLOCK = { CHANGED_LH(C,0) }

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.